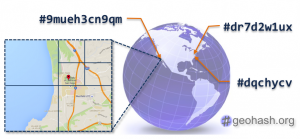

Spatiotemporal analytics — the time and place that you tweet, post, and login — is getting increased interest in data science research. Geohash is a novel and efficient way to provide a location in lieu providing a latitude and longitude. As described in the recently published paper, “Spatial Predicates Evaluation in the Geohash Domain Using Reconfigurable Hardware””, Geohash operations are ripe for implementation on an FPGA due to its bit-level encoding system. This paper was published at the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM). Dajung worked on this research project last summer during her internship at IBM Research. Dajung presented the work at FCCM. Congrats to Dajung and her co-authors Roger Moussalli, Sameh Asaad, and Mudhakar Srivatsa.

Spatiotemporal analytics — the time and place that you tweet, post, and login — is getting increased interest in data science research. Geohash is a novel and efficient way to provide a location in lieu providing a latitude and longitude. As described in the recently published paper, “Spatial Predicates Evaluation in the Geohash Domain Using Reconfigurable Hardware””, Geohash operations are ripe for implementation on an FPGA due to its bit-level encoding system. This paper was published at the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM). Dajung worked on this research project last summer during her internship at IBM Research. Dajung presented the work at FCCM. Congrats to Dajung and her co-authors Roger Moussalli, Sameh Asaad, and Mudhakar Srivatsa.

Author Archives: Ryan

Tinker @ FCCM

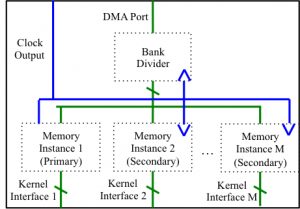

Our paper, Tinker: Generating Custom Memory Architectures for Altera’s OpenCL Compiler was accepted at IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)! Deploying High Level Synthesis hardware design tools and integrating them with existing interfaces is a major challenge. In this paper we introduce Tinker, an open-source Board Support Package generator for Altera’s OpenCL Compiler. Board Support Packages define memory, communication, and other ports for easy integration with high level synthesis cores. Tinker abstracts the low-level hardware details of hardware development when creating board support packages and greatly increases the flexibility of OpenCL development. Tinker allows users to generate custom memory architectures, providing a new method for kernel optimization that was not available before. Congratulations to the authors: Dustin, Matt, Jeremy, Kevin, and Ryan!

Our paper, Tinker: Generating Custom Memory Architectures for Altera’s OpenCL Compiler was accepted at IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)! Deploying High Level Synthesis hardware design tools and integrating them with existing interfaces is a major challenge. In this paper we introduce Tinker, an open-source Board Support Package generator for Altera’s OpenCL Compiler. Board Support Packages define memory, communication, and other ports for easy integration with high level synthesis cores. Tinker abstracts the low-level hardware details of hardware development when creating board support packages and greatly increases the flexibility of OpenCL development. Tinker allows users to generate custom memory architectures, providing a new method for kernel optimization that was not available before. Congratulations to the authors: Dustin, Matt, Jeremy, Kevin, and Ryan!

You can download Tinker from the Git Repository: Tinker Git Repo

Antonella Awarded Explorers Club Grant

Antonella was recently named a recipient of The Explorers Club 2016 Exploration Fund Grant, for her work developing technologies to monitor the endangered vaquita porpoise. This highly-competitive grant is intended to fund “exploration and field research for those who are just beginning their research careers.” The grant will fund her continuing fieldwork in Mexico, using drones and underwater cameras in an effort to capture the first-ever underwater photos of the vaquita. This summer, Antonella will travel back to San Felipe, Baja California, to deploy the SphereCam and other technologies she has engineered. This work will provide leading vaquita researchers with a better understanding of vaquita and its behavior.

Antonella was recently named a recipient of The Explorers Club 2016 Exploration Fund Grant, for her work developing technologies to monitor the endangered vaquita porpoise. This highly-competitive grant is intended to fund “exploration and field research for those who are just beginning their research careers.” The grant will fund her continuing fieldwork in Mexico, using drones and underwater cameras in an effort to capture the first-ever underwater photos of the vaquita. This summer, Antonella will travel back to San Felipe, Baja California, to deploy the SphereCam and other technologies she has engineered. This work will provide leading vaquita researchers with a better understanding of vaquita and its behavior.

Outstanding Community Leader Award

Dustin was recognized with the GSA Outstanding Community Leader Award. This is given by the UCSD Graduate Student Association. This award “honors a UC-San Diego student, staff, or faculty who has displayed unwavering dedication to improving and organizing their community. Through diligent attention to organization and motivation, the awardee has made significant and tangible advances in the lives of their colleagues or neighbors in the UC-San Diego community.” Dustin has done a number of things to make the CSE community better and stronger including aiding in the renovation of Chez Bob and helping organize the prospective graduate student visit day. Congratulations Dustin!

Dustin was recognized with the GSA Outstanding Community Leader Award. This is given by the UCSD Graduate Student Association. This award “honors a UC-San Diego student, staff, or faculty who has displayed unwavering dedication to improving and organizing their community. Through diligent attention to organization and motivation, the awardee has made significant and tangible advances in the lives of their colleagues or neighbors in the UC-San Diego community.” Dustin has done a number of things to make the CSE community better and stronger including aiding in the renovation of Chez Bob and helping organize the prospective graduate student visit day. Congratulations Dustin!

Michael Barrow awarded Engineering Leadership Fellowship

Michael was awarded one of the three fellowships this year in recognition of his collaborations with the medical school, structural, mechanical, and computer science departments to improve patient safety in minimally invasive surgery as well as his work with the NSF supported Early Research Scholarship Program leading 8 teams of undergraduate students. The purpose of the awards program is to reward and recognize successful leaders and to promote positive role models for Jacobs School of Engineering students. Recipients of the award are first nominated by mentors and are then chosen through a competitive selection process. The selection focuses on demonstrated excellence in leadership, engineering ability, communication skills and teamwork.

Michael was awarded one of the three fellowships this year in recognition of his collaborations with the medical school, structural, mechanical, and computer science departments to improve patient safety in minimally invasive surgery as well as his work with the NSF supported Early Research Scholarship Program leading 8 teams of undergraduate students. The purpose of the awards program is to reward and recognize successful leaders and to promote positive role models for Jacobs School of Engineering students. Recipients of the award are first nominated by mentors and are then chosen through a competitive selection process. The selection focuses on demonstrated excellence in leadership, engineering ability, communication skills and teamwork.

National Science Foundation Award for VeriDrone Project

The Cyber-Physical Systems program at the National Science Foundation (NSF) provided a three year grant to develop techniques to develop techniques to insure the correctness, safety, and security of unmanned aerial vehicles or “drones”. We will study verification techniques that look at the hardware and flight control software and their interactions with the sensors and actuators. We aim to insure that the drone is unable to violate properties such as “it should not fly above 500 feet (the FAA mandated limit)” and “it must not enter restricted geographical region (for example, national parks where drones are no illegal to fly”). The grant is headed by Professor Sorin Lerner and in collaboration with Professor Miroslav Kristic. For more information about the project, check out the github page and the NSF award announcement.

The Cyber-Physical Systems program at the National Science Foundation (NSF) provided a three year grant to develop techniques to develop techniques to insure the correctness, safety, and security of unmanned aerial vehicles or “drones”. We will study verification techniques that look at the hardware and flight control software and their interactions with the sensors and actuators. We aim to insure that the drone is unable to violate properties such as “it should not fly above 500 feet (the FAA mandated limit)” and “it must not enter restricted geographical region (for example, national parks where drones are no illegal to fly”). The grant is headed by Professor Sorin Lerner and in collaboration with Professor Miroslav Kristic. For more information about the project, check out the github page and the NSF award announcement.

Local Middle School Students Inspired by Research Projects

In celebration of Engineering Week, the Kastner Research Group participated in the Inspire program. Inspire is designed to introduce approximately 400+ middle school students to university-level engineering, via lab tours and a variety of hands-on projects. This event is hosted by the Triton Engineering Student Council (TESC). Pictured are PhD students Ali Khodamoradi and Dajung Lee sharing an FPGA implementation of GNU Radio. Quentin Gautier and Alexandria Shearer, also pictured, explain the nuances of structure from motion and lidar. The Kastner Research Group has a keen interest in giving students in the local community the chance to explore UC San Diego and experience engineering firsthand.

In celebration of Engineering Week, the Kastner Research Group participated in the Inspire program. Inspire is designed to introduce approximately 400+ middle school students to university-level engineering, via lab tours and a variety of hands-on projects. This event is hosted by the Triton Engineering Student Council (TESC). Pictured are PhD students Ali Khodamoradi and Dajung Lee sharing an FPGA implementation of GNU Radio. Quentin Gautier and Alexandria Shearer, also pictured, explain the nuances of structure from motion and lidar. The Kastner Research Group has a keen interest in giving students in the local community the chance to explore UC San Diego and experience engineering firsthand.

Alexandria Highlighted in Santa Clara University Article

Alexandria was a featured story in Santa Clara University’s Engineering School website following her NSF Graduate Research Fellowship Award. Barely six years ago she began her undergraduate career at Santa Clara University with little to no technical literacy. Now her work is taking flight here with the Kastner Research Group. The article is an interview that discusses her work on Aerial LIDAR Scanning over a Guatemalan jungle, her plans following advancement to candidacy, and her advice for incoming computer science and engineering students.

Alexandria was a featured story in Santa Clara University’s Engineering School website following her NSF Graduate Research Fellowship Award. Barely six years ago she began her undergraduate career at Santa Clara University with little to no technical literacy. Now her work is taking flight here with the Kastner Research Group. The article is an interview that discusses her work on Aerial LIDAR Scanning over a Guatemalan jungle, her plans following advancement to candidacy, and her advice for incoming computer science and engineering students.

Links: Santa Clara University Interview, Alexandria Shearer Webpage

Amazon Web Services Grant: Exploring Hardware in the Cloud

We received an Amazon Web Services (AWS) Grant for our research on how to use machine learning to aid design space exploration of the high level synthesis (HLS) tools. Compiling a design to an FPGA is extremely time consuming (it can take days of compute time for compilation). Moreover, our research requires tens of thousands of these synthesis runs for the purpose of training better machine learning strategies. Collecting this amount of data could take several years even on a high-end workstation. For this reason, it was almost impossible to collect enough data for our research on the computer equipment in our lab. Now, with this grant ($15,300 of AWS credits), we are able to collect this data by running the process on AWS in parallel. The AWS parallel computing power will significantly speedup this process. Thanks to the AWS academic program, we now have the opportunity to further understand the nature of the hardware design spaces and build better machine learning strategies to aid application designers in the future. For those looking for more details, our initial research efforts in this space has been accepted at DATE 2016 in the article “Adaptive Threshold Non-Pareto Elimination: Re-thinking Machine Learning for System Level Design Space Exploration on FPGAs”.

We received an Amazon Web Services (AWS) Grant for our research on how to use machine learning to aid design space exploration of the high level synthesis (HLS) tools. Compiling a design to an FPGA is extremely time consuming (it can take days of compute time for compilation). Moreover, our research requires tens of thousands of these synthesis runs for the purpose of training better machine learning strategies. Collecting this amount of data could take several years even on a high-end workstation. For this reason, it was almost impossible to collect enough data for our research on the computer equipment in our lab. Now, with this grant ($15,300 of AWS credits), we are able to collect this data by running the process on AWS in parallel. The AWS parallel computing power will significantly speedup this process. Thanks to the AWS academic program, we now have the opportunity to further understand the nature of the hardware design spaces and build better machine learning strategies to aid application designers in the future. For those looking for more details, our initial research efforts in this space has been accepted at DATE 2016 in the article “Adaptive Threshold Non-Pareto Elimination: Re-thinking Machine Learning for System Level Design Space Exploration on FPGAs”.

New PhD Student: Antonella Wilby

This winter quarter, we welcome a “new” PhD student to our group. But Antonella is fair from a stranger; she has been working with the Engineers for Exploration program for several years now as an undergraduate. Antonella’s work has mostly focused on underwater monitoring. She worked on a variety of different remote sensing projects. Her most recent efforts on focused on saving the vaquita — the most endangered marine mammal in the world. As part of this work, she was named a National Geographic Young Explorer. Her recent post on National Geographic Ocean Views blog provides more details on her efforts. The picture to shows her testing an early version of the SphereCam which is being used to capture photographs of the vaquita. In addition to her National Geographic Award, she received a National Science Foundation Graduate Fellow Honorable Mention in 2015, and was the second UCSD CSE student to be UCSD Sloan Scholar (the first is Kastner Research Group member Jeremy Blackstone). Welcome to the ranks of the graduate students Antonella!

This winter quarter, we welcome a “new” PhD student to our group. But Antonella is fair from a stranger; she has been working with the Engineers for Exploration program for several years now as an undergraduate. Antonella’s work has mostly focused on underwater monitoring. She worked on a variety of different remote sensing projects. Her most recent efforts on focused on saving the vaquita — the most endangered marine mammal in the world. As part of this work, she was named a National Geographic Young Explorer. Her recent post on National Geographic Ocean Views blog provides more details on her efforts. The picture to shows her testing an early version of the SphereCam which is being used to capture photographs of the vaquita. In addition to her National Geographic Award, she received a National Science Foundation Graduate Fellow Honorable Mention in 2015, and was the second UCSD CSE student to be UCSD Sloan Scholar (the first is Kastner Research Group member Jeremy Blackstone). Welcome to the ranks of the graduate students Antonella!

Links:

Antonella’s personal website

National Geographic Ocean Voices blog