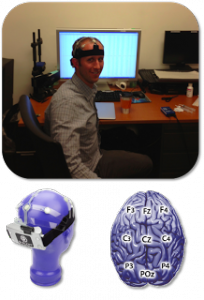

It may seem like science fiction, but we showed that it is possible to use sensors to monitor your brain waves and quickly detect underwater mines in sonar images. We combined techniques from computer vision with cutting edge classification of focal interest of human operators via electroencephalography (EEG) analysis, i.e., the recording of electrical activity along the scalp. This is the first approach for using EEG in this application.

It may seem like science fiction, but we showed that it is possible to use sensors to monitor your brain waves and quickly detect underwater mines in sonar images. We combined techniques from computer vision with cutting edge classification of focal interest of human operators via electroencephalography (EEG) analysis, i.e., the recording of electrical activity along the scalp. This is the first approach for using EEG in this application.

These ideas are detailed in our upcoming journal paper, “A Brain-Computer Interface (BCI) for the Detection of Mine-Like Objects in Side Scan Sonar Imagery”, that has been accepted as a full article in the Journal of Oceanic Engineering. Congrats are in order to the authors: Christopher Barngrover, Alric Althoff, Paul DeGuzman, and Ryan Kastner. Special thanks to Neuromatters for the support with the EEG analysis tools and to Advanced Brain Monitoring for the use of the EEG sensors and hardware. The picture shows Dr. Chris Barngrover stylishly sporting the EEG cap at Neuromatters in New York City.