Our friends and collaborators at USC created a short video on the recent field season at the Maya site El Zotz in Guatemala. We spent about a week there developing 3D models of the various artifacts and excavations. See if you can find the Kastner Research Group members in the video.

Monthly Archives: December 2015

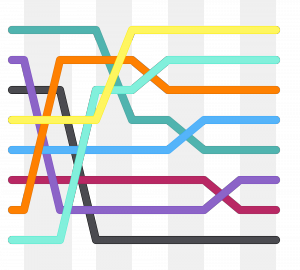

High Speed Sorting Paper Accepted to ISFPGA

Our paper “Resolve: Generation of High-Performance Sorting Architectures from High-Level Synthesis” was accepted as a full paper at the International Symposium on Field-Programmable Gate Arrays (ISFPGA) to be held in Monterey, CA in February 2016. Our Resolve framework allows designers to quickly create generate architectures to meet the requirements of the performance at hand. In particular, Resolve provides ten highly optimized basic sorting architectures; it easily composes basic architectures to generate hybrid sorting architectures; and it enables non-hardware experts to quickly design efficient hardware designs, and easily develop customized heterogeneous FPGA/CPU systems.

Our paper “Resolve: Generation of High-Performance Sorting Architectures from High-Level Synthesis” was accepted as a full paper at the International Symposium on Field-Programmable Gate Arrays (ISFPGA) to be held in Monterey, CA in February 2016. Our Resolve framework allows designers to quickly create generate architectures to meet the requirements of the performance at hand. In particular, Resolve provides ten highly optimized basic sorting architectures; it easily composes basic architectures to generate hybrid sorting architectures; and it enables non-hardware experts to quickly design efficient hardware designs, and easily develop customized heterogeneous FPGA/CPU systems.

This was the “final” paper from Dr. Janarbek Matai’s PhD work. He provided this inspirational quote and sage piece of advice to the other members of the Kastner Research Group: “In case if you are … wondering how it feels like writing a paper after graduation, I will tell you. The function of pain is not logarithmic anymore, it is exponential. … Publish before your graduation.” Wise words indeed. Congrats to Janarbek for not having to feel the logarithmic or exponential pain anymore. And to the other authors (Dustin Richmond, Dajung Lee, Zac Blair, Qiongzhi Wu, Amin Abazari, and Ryan Kastner) most of which have a lot of pain to look forward to in the future.