#### UNIVERSITY OF CALIFORNIA SAN DIEGO

Using Blinking to Mitigate Passive Side Channel Attacks and Fault Attacks

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science

by

Jeremy Blackstone

## Committee in charge:

Professor Ryan Kastner, Chair Professor Sean Gao Professor Truong Nguyen Professor Lawrence Saul Professor Geoff Voelker

Copyright

Jeremy Blackstone, 2021

All rights reserved.

| The Dissertation of Jeremy Blackstone is approved, and it is acceptable in quality |

|------------------------------------------------------------------------------------|

| and form for publication on microfilm and electronically.                          |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| University of California San Diego                                                 |

| 2021                                                                               |

|                                                                                    |

|                                                                                    |

|                                                                                    |

# **DEDICATION**

To my wife Abigail Blackstone for reading and giving feedback on research papers regarding topics she is unfamiliar with and being the inspiration to finish them.

# EPIGRAPH

Failure is simply the opportunity to begin again, this time more intelligently.

Henry Ford

# TABLE OF CONTENTS

| Disserta  | tion Approval Page                     | iii  |

|-----------|----------------------------------------|------|

| Dedicati  | on                                     | iv   |

| Epigrapl  | h                                      | V    |

| Table of  | Contents                               | vi   |

| List of F | Figures                                | ix   |

| List of T | Tables                                 | хi   |

| Acknow    | ledgements                             | xii  |

| Vita      |                                        | xiii |

| Abstract  | of the Dissertation                    | xiv  |

| Chapter   | 1 Background                           | 1    |

| 1.1       | Cryptographic Algorithms               | 1    |

|           | 1.1.1 AES                              | 2    |

|           | 1.1.2 PRESENT                          | 4    |

| 1.2       | Passive Side Channel Attacks           | 6    |

|           | 1.2.1 Power Analysis                   | 6    |

|           | 1.2.2 Electromagnetic Analysis Attacks | 10   |

| 1.3       | Fault Analysis Attacks                 | 12   |

|           | 1.3.1 Differential Fault Analysis      | 12   |

|           | 1.3.2 Fault Sensitivity Analysis       | 23   |

|           | 1.3.3 Biased Fault Analysis            | 26   |

|           | 1.3.4 Combined Fault Analysis          | 28   |

| 1.4       | Threat Model                           | 29   |

| 1.5       | Passive Side Channel Countermeasures   | 30   |

| 1.6       | Fault Analysis Countermeasures         | 30   |

| 1.0       | 1.6.1 Masking                          | 30   |

|           | 1.6.2 Time Redundancy                  | 31   |

|           | 1.6.3 Error Detection Codes            | 31   |

|           | 1.6.4 CAMFAS                           | 31   |

| 1.7       | Contributions                          | 32   |

| 1./       | Contributions                          | 32   |

| Chapter   | 2 Introduction                         | 34   |

| Chapter   | 3 Power Analysis Mitigation            | 37   |

| 3.1       | Switched Capacitor                     | 39   |

| 3.2       | Joint Mutual Information               | 40   |

| 3.3     | Stalling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42 |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|         | 3.3.1 Stalling Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44 |  |  |

|         | 3.3.2 Stalling Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45 |  |  |

| 3.4     | Stalling Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47 |  |  |

|         | 3.4.1 Blink and Recharge Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |  |  |

|         | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49 |  |  |

| 3.5     | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50 |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| 3.6     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| 3.7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| Chapter | 4 Fault Analysis Mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58 |  |  |

| 4.1     | Fault Attacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |  |  |

| 4.2     | Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |  |  |

|         | 4.2.1 Power Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62 |  |  |

|         | 4.2.2 Clock Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |  |  |

| 4.3     | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64 |  |  |

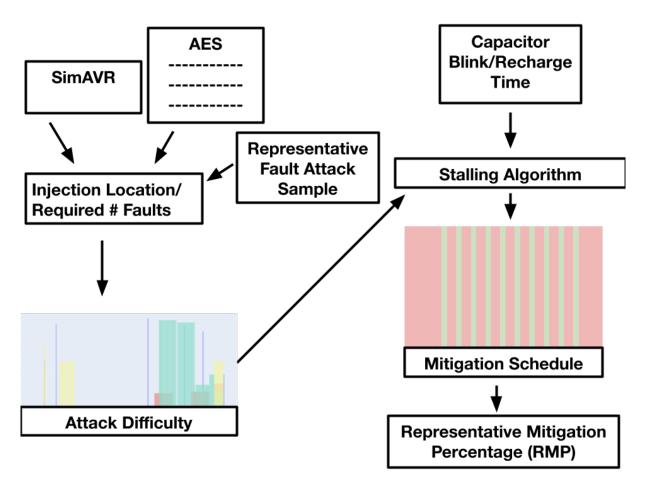

|         | 4.3.1 Blinking Performance Lower Bound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |  |  |

|         | 4.3.2 Mitigation Technique Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |  |  |

| 4.4     | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69 |  |  |

| 4.5     | 3.3.1       Stalling Algorithm       45         3.3.2       Stalling Parameters       47         3.4.1       Blink and Recharge Time       47         3.4.2       On-Chip Capacitance       48         3.4.3       Clock Speed       48         3.4.4       Multiple Blink Times       49         5.5       Results       49         3.5.1       Experimental Setup       49         3.5.2       Blink/Recharge Time Calculations       50         3.5.3       Design Exploration for Stalling       51         6       Conclusion       57         7.7       Acknowledgements       57         ster 4       Fault Analysis Mitigation       58         1. Fault Attacks       60         2. Isolation       62         4.2.1       Power Isolation       62         4.2.2       Clock Isolation       63         3.3       Results       64         4.3.1       Blinking Performance Lower Bound       64         4.3.2       Mitigation Technique Comparison       67         oter 5       EM Analysis Mitigation       71         oter 5       EM Analysis Mitigation       71         1. STELLAR           |    |  |  |

| ~.      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| Chapter | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |

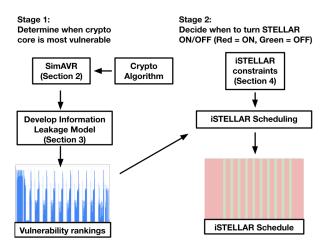

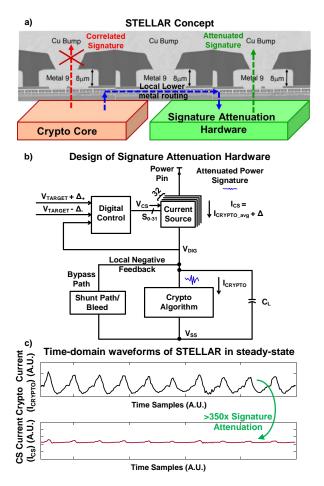

| 5.1     | 3.4.2 On-Chip Capacitance       48         3.4.3 Clock Speed       48         3.4.4 Multiple Blink Times       49         Results       49         3.5.1 Experimental Setup       49         3.5.2 Blink/Recharge Time Calculations       50         3.5.3 Design Exploration for Stalling       51         Conclusion       57         Acknowledgements       57         r 4 Fault Analysis Mitigation       58         Fault Attacks       60         Isolation       62         4.2.1 Power Isolation       62         4.2.2 Clock Isolation       63         Results       64         4.3.1 Blinking Performance Lower Bound       64         4.3.2 Mitigation Technique Comparison       67         Conclusions       69         Acknowledgements       70         r 5 EM Analysis Mitigation       71         STELLAR       73         Motivation       74         Security Evaluation       75         5.3.1 Joint Mutual Information (JMI)       75         5.3.2 Minimum Traces to Disclosure (MTD)       78         1STELLAR       80         5.4.1 Constraints       80         5.4.2 ISTELLAR Sche |    |  |  |

| 5.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| 5.3     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |

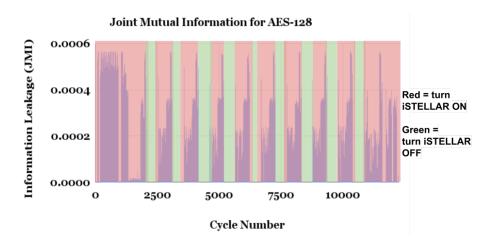

|         | ` /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |  |  |

|         | 5.3.2 Minimum Traces to Disclosure (MTD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |

| 5.4     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

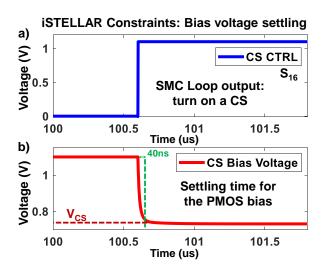

|         | 5.4.2 iSTELLAR Lower Bound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81 |  |  |

|         | 5.4.3 iSTELLAR Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82 |  |  |

| 5.5     | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84 |  |  |

|         | 5.5.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84 |  |  |

|         | 5.5.2 Power vs Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85 |  |  |

|         | 5.5.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87 |  |  |

| 5.6     | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88 |  |  |

| 5.7     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89 |  |  |

| 5.8     | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89 |  |  |

| Chapter 6    | Conclusion | 90 |

|--------------|------------|----|

| Bibliography |            | 91 |

# LIST OF FIGURES

| Figure 1.1.  | AES's S-box                                         | 2  |

|--------------|-----------------------------------------------------|----|

| Figure 1.2.  | Shift Rows layer                                    | 3  |

| Figure 1.3.  | Mix Columns layer                                   | 3  |

| Figure 1.4.  | Key Scheduling Algorithm                            | 4  |

| Figure 1.5.  | PRESENT key shift operation                         | 5  |

| Figure 1.6.  | Differential Power Analysis(DPA) example            | 8  |

| Figure 1.7.  | Differential Electromagnetic Analysis(DEMA) example | 12 |

| Figure 1.8.  | Difference between ciphertexts                      | 14 |

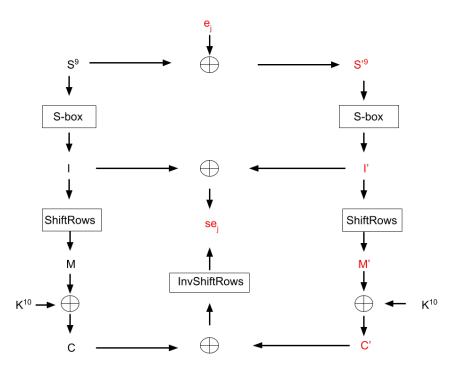

| Figure 1.9.  | DFA key recovery diagram                            | 15 |

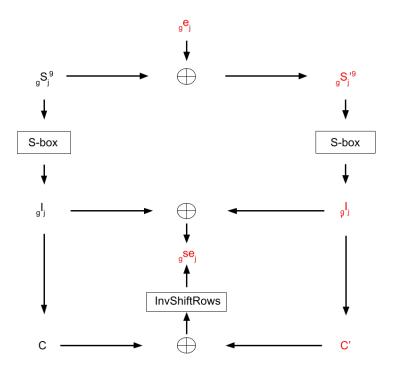

| Figure 1.10. | Generalized DFA                                     | 18 |

| Figure 1.11. | Maksed DFA diagram                                  | 19 |

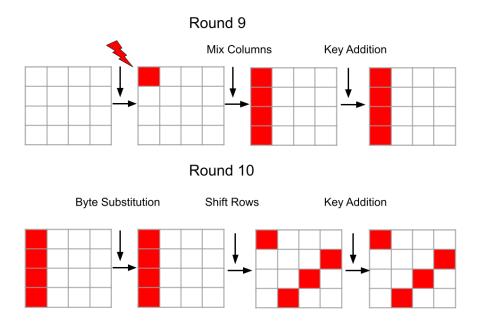

| Figure 1.12. | Single Fault DFA fault propagation                  | 20 |

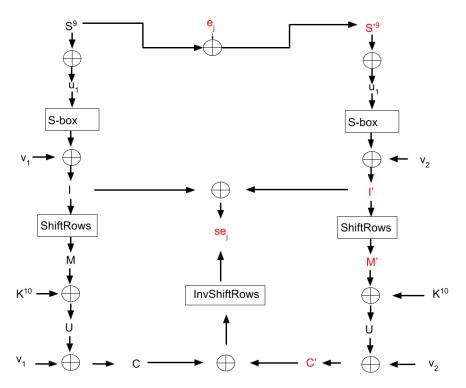

| Figure 1.13. | Single Fault DFA                                    | 22 |

| Figure 1.14. | FSA example part 1                                  | 24 |

| Figure 1.15. | FSA example part 2                                  | 25 |

| Figure 1.16. | DFIA attack part 1                                  | 27 |

| Figure 1.17. | DFIA attack part 2                                  | 28 |

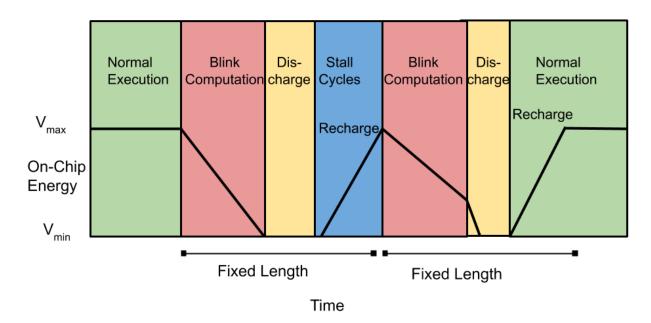

| Figure 2.1.  | blinking overview                                   | 35 |

| Figure 2.2.  | stalling overview                                   | 36 |

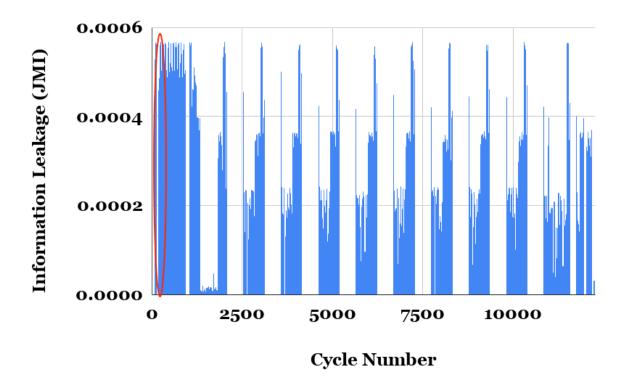

| Figure 3.1.  | JMI example 1                                       | 38 |

| Figure 3.2.  | blinking process 1                                  | 40 |

| Figure 3.3.  | stalling motivation 1                               | 43 |

| Figure 3.4.  | stalling motivation 2                               | 44 |

| Figure 3.5. | stalling process 1                                                           | 45 |

|-------------|------------------------------------------------------------------------------|----|

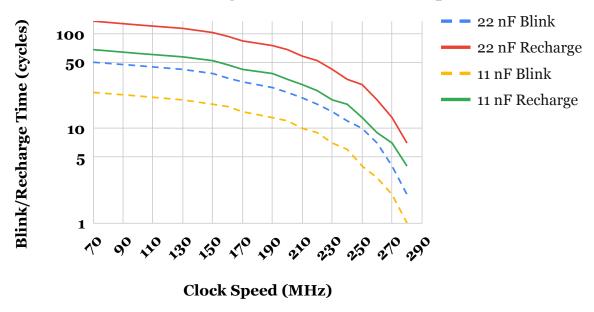

| Figure 3.6. | capacitance 1                                                                | 51 |

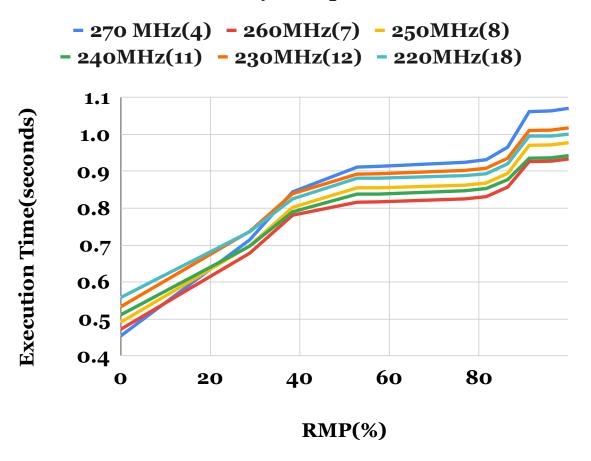

| Figure 3.7. | example stalling schedule 1                                                  | 52 |

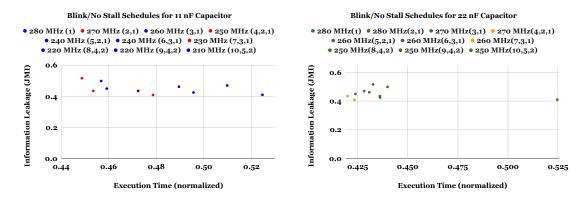

| Figure 3.8. | blinking schedules                                                           | 53 |

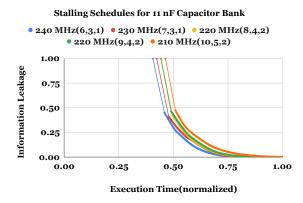

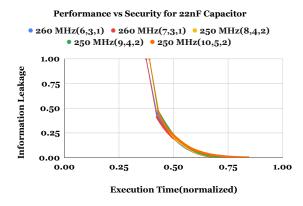

| Figure 3.9. |                                                                              | 54 |

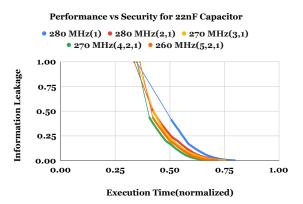

| Figure 4.1. | fault blinking overview                                                      | 59 |

| Figure 4.2. | The lower bound for performance with blinking is between 220 MHz and 270 MHz | 65 |

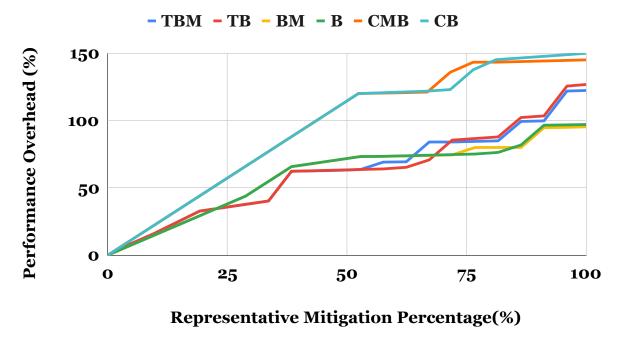

| Figure 4.3. | Results for Combined Fault Mitigation Strategies                             | 66 |

| Figure 5.1. | iSTELLAR overview                                                            | 72 |

| Figure 5.2. | STELLAR 1                                                                    | 73 |

| Figure 5.3. | JMI example 2                                                                | 75 |

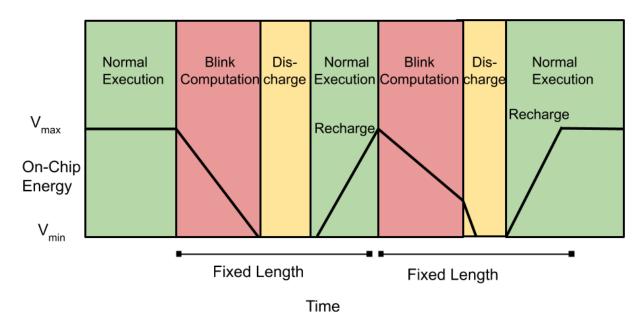

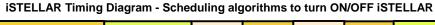

| Figure 5.4. | iSTELLAR timing diagram                                                      | 76 |

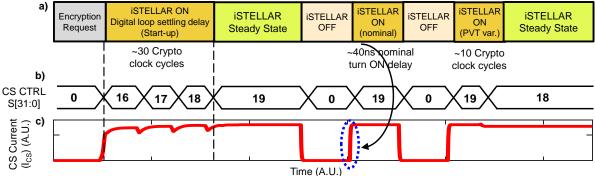

| Figure 5.5. | turn on delay                                                                | 79 |

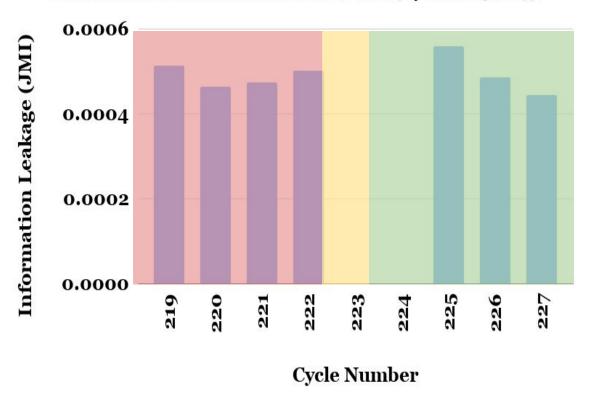

| Figure 5.6. | iSTELLAR motivation 1                                                        | 83 |

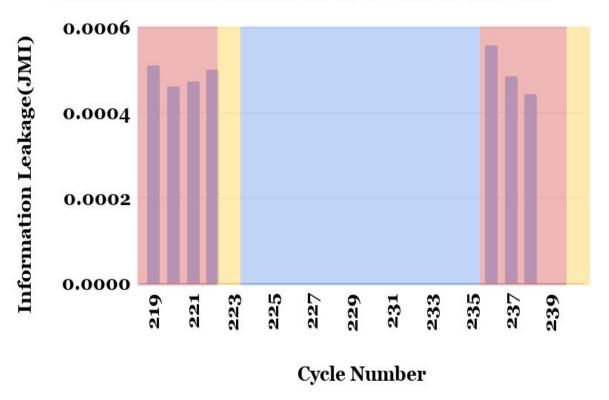

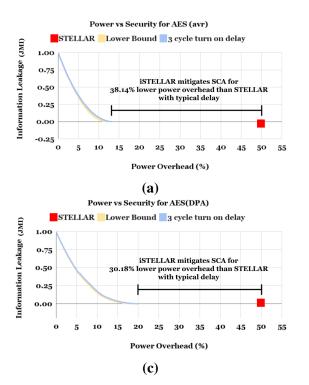

| Figure 5.7. | iSTELLAR results 1                                                           | 85 |

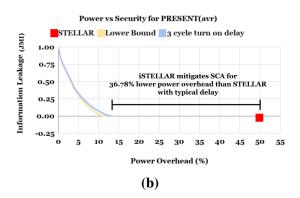

| Figure 5.8. | iSTELLAR results 2                                                           | 86 |

# LIST OF TABLES

| Table 1.1. | PRESENT's S-Box                                                    | 5  |

|------------|--------------------------------------------------------------------|----|

| Table 1.2. | PRESENT's permutation layer places each bit i in new position P(i) | 6  |

| Table 3.1. | 11 nF Results                                                      | 56 |

| Table 3.2. | 22 nF Results                                                      | 56 |

| Table 4.1. | list of fault attacks                                              | 61 |

| Table 4.2. | combined fault mitigation strategies                               | 67 |

| Table 4.3. | list of fault attacks 2                                            | 68 |

| Table 5.1. | Power Overhead for iSTELLAR                                        | 87 |

#### **ACKNOWLEDGEMENTS**

I would like to acknowledge Professor Ryan Kastner for his support as the chair of my committee. Through multiple drafts, his guidance has proved to be invaluable.

Chapter 3, "Power Analysis Mitigation" is based on "Using Stalls to Minimize Information Leakage". It is coauthored with Alric Althoff, Scott Davidson, Dustin Richmond, Michael Taylor and Ryan Kastner and is currently being prepared for submission for publication of the material. The dissertation author was the primary author of this chapter.

Chapter 4, "Fault Analysis Mitigation" is based on "Using Intermittent Isolation To Mitigate Fault Attacks". It is coauthored with Alric Althoff, Scott Davidson, Dustin Richmond, Michael Taylor and Ryan Kastner and is currently being prepared for submission for publication of the material. The dissertation author was the primary author of this chapter.

Chapter 5, "EM Analysis Mitigation" is based on "iSTELLAR: intermittent Signature aTenuation Embedded CRYPTO with Low-Level metAl Routing". It is coauthored with Debayan Das, Shreyas Sen and Ryan Kastner and is currently being prepared for submission for publication of the material. The dissertation author was the primary author of this chapter.

# VITA

| 2014 | B. S. in Systems and Computer Science, Howard University, Washington, DC |

|------|--------------------------------------------------------------------------|

| 2015 | M. S. in Systems and Computer Science, Howard University, Washington, DC |

| 2021 | Ph. D. in Computer Science, University of California, San Diego          |

#### ABSTRACT OF THE DISSERTATION

Using Blinking to Mitigate Passive Side Channel Attacks and Fault Attacks

by

Jeremy Blackstone

Doctor of Philosophy in Computer Science

University of California San Diego, 2021

Professor Ryan Kastner, Chair

Ignoring security concerns when building digital hardware allows for malicious parties to take advantage of vulnerabilities to gain access to secret information and manipulate systems. This is unacceptable because of the disastrous results of attackers compromising consumer products such as cell phones, smart cards and automobiles. To this end, researchers have developed numerous mathematically secure cryptographic algorithms.

Unfortunately, side channel analysis (SCA) attacks bypass these algorithms by monitoring the effects of the algorithm on a physical platform through power consumption, electromagnetic emanations (EM), or subjecting it to fault injection. These effects are referred to as side channels. By analyzing side channels, an attacker is able to discover sensitive information, e.g., extracting

the secret key from a cryptographic algorithm.

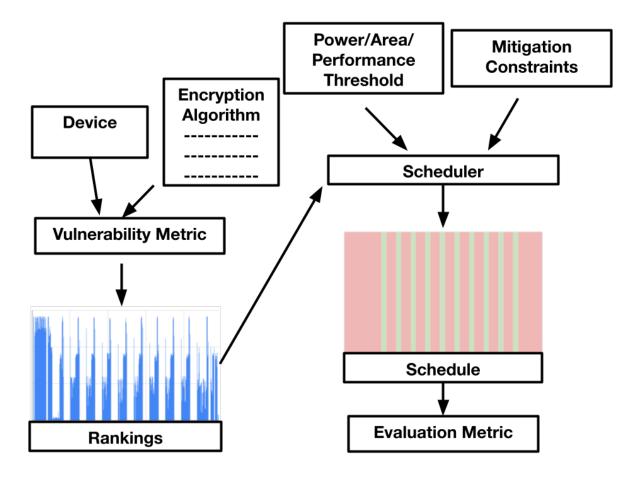

It is shown in [3] that retrieving side channel information is not uniform. Some portions of the execution reveal a large amount of information to an adversary while other portions reveal little to no information to the adversary. However, most SCA countermeasures incur larger than necessary overhead by protecting all portions of the computation. One way to reduce overhead is through a methodology called blinking. Blinking identifies the most critical points in time for a cryptographic computation and performs isolation to prevent an adversary from observing or modifying any information. This thesis proposes using blinking in a variety of different scenarios and provides analysis so hardware designers can make informed decisions on how to balance the performance, area overhead, power consumption and security.

First, this thesis provides analysis on using blinking to mitigate power analysis attacks with an on-chip capacitor. Next, this thesis shows how the same on-chip capacitor can be used to protect against differential fault analysis, fault sensitivity analysis, biased fault analysis and combined fault analysis. Finally, this thesis demonstrates how blinking can be used to attenuate EM analysis.

# Chapter 1

# **Background**

# 1.1 Cryptographic Algorithms

Cryptographic algorithms are essential to protecting integrity and confidentiality for data. These algorithms keep data secure using hardware specifically designed to execute them in order to perform operations as quickly as possible[8, 45]. Many products including smart cards, mobile devices and TV set-top boxes implement symmetric encryption algorithms such as the Advanced Encryption Standard(AES).

Symmetric encryption hinges on the idea that a secret key can introduce uncertainty into a encryption algorithm[135]. Sharing the secret key only with authorized users allows for them to access the data while disallowing access to unauthorized users. Cryptography focuses on ensuring that the computational effort of determining this secret key using a brute force search is exponentially dependent on the key size to the point that it is not feasible for an adversary to accomplish it using modern computing resources.

Side channel attacks allow an adversary to use information from the algorithm's physical implementation on hardware to extract secret data and assist in finding the key by reducing the key space. Side channel attacks are important because they undermine the algorithmic complexity required to keep the secret key secure. The key space is important because it is the set keys that will be used in an exhaustive search for the secret key.

|   | 0  | 1          | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | A  | В  | C  | D  | E  | F          |

|---|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|------------|

| 0 | 63 | 7c         | 77 | 7B | F2 | 6B | 6F | C5 | 30 | 01 | 67 | 2B | FE | D7 | AB | 76         |

| 1 | CA | 82         | C9 | 7D | FA | 59 | 47 | F0 | AD | D4 | A2 | AF | 9C | A4 | 72 | <b>C</b> 0 |

| 2 | В7 | FD         | 93 | 26 | 36 | 3F | F7 | CC | 34 | A5 | E5 | F1 | 71 | D8 | 31 | 15         |

| 3 | 04 | C7         | 23 | C3 | 18 | 96 | 05 | 9A | 07 | 12 | 80 | E2 | EB | 27 | B2 | 75         |

| 4 | 09 | 83         | 2C | 1A | 1B | 6E | 5A | A0 | 52 | 3B | D6 | В3 | 29 | E3 | 2F | 84         |

| 5 | 53 | D1         | 00 | ED | 20 | FC | B1 | 5B | 6A | СВ | BE | 39 | 4A | 4C | 58 | CF         |

| 6 | D0 | EF         | AA | FB | 43 | 4D | 33 | 85 | 45 | F9 | 02 | 7F | 50 | 3C | 9F | A8         |

| 7 | 51 | A3         | 40 | 8F | 92 | 9D | 38 | F5 | ВС | В6 | DA | 21 | 10 | FF | F3 | D2         |

| 8 | CD | 0C         | 13 | EC | 5F | 97 | 44 | 17 | C4 | A7 | 7E | 3D | 64 | 5D | 19 | 73         |

| 9 | 60 | 81         | 4F | DC | 22 | 2A | 90 | 88 | 46 | EE | В8 | 14 | DE | 5E | 0B | DB         |

| A | E0 | 32         | 3A | 0A | 49 | 06 | 24 | 5C | C2 | D3 | AC | 62 | 91 | 95 | E4 | 79         |

| В | E7 | C8         | 37 | 6D | 8D | D5 | 4E | A9 | 6C | 56 | F4 | EA | 65 | 7A | AE | 08         |

| С | BA | 78         | 25 | 2E | 1C | A6 | В4 | C6 | E8 | DD | 74 | 1F | 4B | BD | 8B | 8A         |

| D | 70 | 3E         | В5 | 66 | 48 | 03 | F6 | 0E | 61 | 35 | 57 | В9 | 86 | C1 | 1D | 9E         |

| Е | E1 | F8         | 98 | 11 | 69 | D9 | 8E | 94 | 9B | 1E | 87 | E9 | CE | 55 | 28 | DF         |

| F | 8C | <b>A</b> 1 | 89 | 0D | BF | E6 | 42 | 68 | 41 | 99 | 2D | 0F | В0 | 54 | BB | 16         |

|   |    |            |    |    |    |    |    |    |    |    |    |    |    |    |    |            |

Figure 1.1. AES's S-box

#### 1.1.1 **AES**

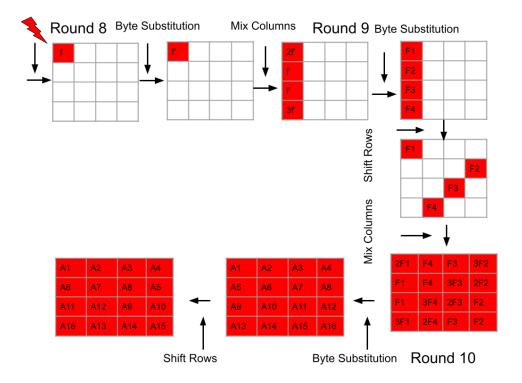

The Advanced Encryption Standard(AES) is a cryptographic algorithm which takes a 128 bit plaintext and encrypts it using a secret key [116]. It is composed of iterations called rounds and the number of rounds corresponds to the key length. If the secret key is 128 bits, there are 10 rounds, if it is 192 bits there are 12 rounds and if it is 256 bits there are 14 rounds. Each round is composed of 4 layers: Byte Substitution, ShiftRows, MixColumns and Key Addition.

When computing AES, the plaintext is first exored with the secret key and sent to the Byte Substitution layer. In this layer, each byte is substituted based on a lookup table called an S-Box as shown in figure 1.1. The first 4 bits of the plaintext are used to determine the column and the last 4 bits are used to determine the row. For example, if the input byte is d7 it will be replaced substituted with the byte 0e.

Next, each byte is considered an element in a 4 x 4 state matrix and sent to the ShiftRows

Figure 1.2. Shift Rows layer

$$\begin{pmatrix} C_0 \\ C_1 \\ C_2 \\ C_3 \end{pmatrix} = \begin{pmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{pmatrix} \cdot \begin{pmatrix} B_0 \\ B_5 \\ B_{10} \\ B_{15} \end{pmatrix}$$

Figure 1.3. Mix Columns layer

layer.

In this layer, the first row of the matrix remains unchanged, the second row is shifted to the left 1 byte, the third row is shifted to the left 2 bytes and the fourth row is shifted to the left 3 bytes as shown in Figure 1.2.

After the ShiftRows layer, the MixColumns layer does matrix multiplication between the current state matrix  $(B_i)$  and the matrix shown in Figure 1.3 to produce a new state matrix  $(C_i)$ .

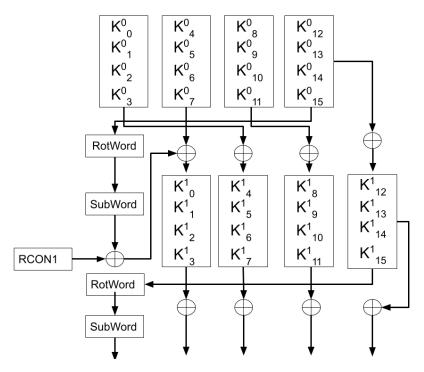

Finally, in the Key Addition layer, each bit is exored with a 16 byte variation of the secret key called a round key. Round keys are generated by a key scheduling algorithm as shown in Figure 1.4. In this algorithm, first the initial key is divided into words and can be considered round key 0. Next, the last word of round key 0 is sent to a RotWord function which shifts the positions of bytes in the word and a SubWord function which sends the word into an S-box. This value is exored with a constant value called RCON to generate the first word of round key 1. The second word is generated by exoring the first word of the current round key and the second word

Figure 1.4. Key Scheduling Algorithm

from round key 0. Each subsequent word is generated by exoring the preceding word from the current round with the parallel word from the previous round. The last word of round key 1 is sent to the RotWord and SubWord functions and this process continues until all 10 round keys have been generated.

#### **1.1.2 PRESENT**

While AES is the preferred algorithm of choice for most applications, it is not best suited for highly resource constrained devices such as RFID tags and sensor networks [16]. To address this problem, PRESENT has been proposed as an ultralightweight block cipher.

PRESENT can be implemented on a 64-bit plaintext with either 80-bit or 128-bit keys. Like AES, PRESENT is also composed of rounds, but it is always 31 rounds regardless of the key length. Each round consists of an AddRoundKey layer, S-box layer and permutation layer.

In the AddRoundKey layer, each bit is exored with a 64 bit variation of the secret key

Figure 1.5. PRESENT key shift operation

**Table 1.1.** PRESENT's S-Box

| X    | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | С | D | Е | F |

|------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S(x) | С | 5 | 6 | В | 9 | 0 | A | D | 3 | Е | F | 8 | 4 | 7 | 1 | 2 |

called a round key. Round keys are generated by a key scheduling algorithm as shown in Figure 1.4.

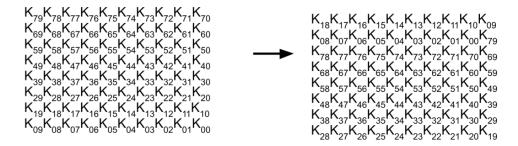

While PRESENT can have an 80bit or 128-bit key, we focus on an example with an 80-bit key. In this algorithm, the 64 leftmost bits of the key (K) are chosen as the initial round key ( $K^0$ ). Next, the key is shifted left by 61 positions as shown in figure 1.5 and table 1.1. Afterwards, the four leftmost bits are substituted through PRESENT's S-Box as shown in equation 1.1. Finally, bits  $K_19K_18K_17K_16K_15$  are exored with the least significant bit of the round counter as shown in equation 1.2 where i is the round number.

$$K_{79}K_{78}K_{77}K_{76} = S(K_{79}K_{78}K_{77}K_{76}) (1.1)$$

$$K_{19}K_{18}K_{17}K_{16}K_{15} = K_{19}K_{18}K_{17}K_{16}K_{15} \oplus i_0 \tag{1.2}$$

In the S-Box layer, each nibble is substituted based on PRESENT's S-box as shown in table 1.1.

In the permutation layer, each bit in the current state is moved to a new position. This is shown in table 1.2 where i is the initial position of the bit and P(i) is the new position of the bit.

**Table 1.2.** PRESENT's permutation layer places each bit i in new position P(i)

| i    | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| P(i) | 0  | 16 | 32 | 48 | 1  | 17 | 33 | 49 | 2  | 18 | 34 | 50 | 3  | 19 | 35 | 51 |

| i    | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| P(i) | 4  | 20 | 36 | 52 | 5  | 21 | 37 | 53 | 6  | 22 | 38 | 54 | 7  | 23 | 39 | 55 |

| i    | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| P(i) | 8  | 24 | 40 | 56 | 9  | 25 | 41 | 57 | 10 | 26 | 42 | 58 | 11 | 27 | 43 | 59 |

| i    | 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| P(i) | 12 | 28 | 44 | 60 | 13 | 29 | 45 | 61 | 14 | 30 | 46 | 62 | 15 | 31 | 47 | 63 |

## 1.2 Passive Side Channel Attacks

### 1.2.1 Power Analysis

Microprocessors are composed of logical gates which behave differently based on the data and instructions they are given as input[5]. This is because power is applied or removed from transistors to hold values or perform an operation on values. Therefore, power consumption contains information about a device's operations because differing behaviors require differing amounts of power to perform. Power analysis attacks correlate power consumption measurements collected during cryptographic computations to a device's operation and secret information[77]. A number of power attacks have been used to reveal the secret key in a variety of scenarios [96, 138, 77, 19, 61, 140, 92, 26, 97, 78, 15, 118, 90, 94]

#### **Simple Power Analysis**

Simple Power Analysis(SPA) is the most basic class of power attacks. These attacks simply observe a power trace, collection of power measurements taken over a period of time, and attempt to derive information from it[77]. SPA uses variations in power to determine sequences of instructions. As an example, an adversary could collect the power measurements for a round of AES and distinguish which cycles are performing Byte Substitution, ShiftRows, MixColumns

and Key Addition [127].

#### **Differential Power Analysis**

While SPA is useful for identifying properties of a cryptogrphic algorithm, in many cases, simply observing a power trace is not sufficient to recover the entire secret key. Differential Power Analysis (DPA) solves this problem by analyzing the differences between power traces. Furthermore, is capable of launching a successful attack even when there is a significant amount of noise in the power measurement. The attacker simply needs to acquire more power measurements to develop a reasonable signal to noise ratio.

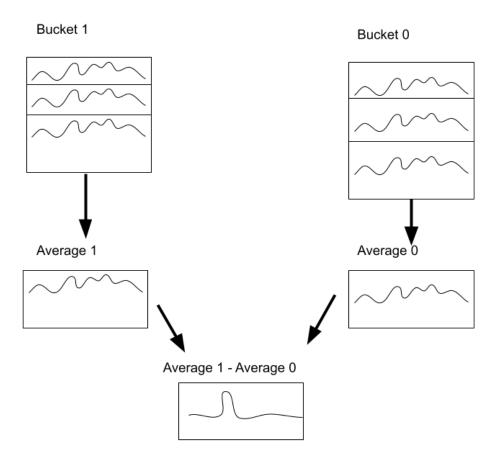

Classical DPA approaches take a univariate approach by choosing a single point in an algorithm's execution, collect a number of traces and divides them into two buckets [87]. The traces are divided into buckets using a selection function which based on the assumption that a device consumes more power changing a bit from 0 to 1 than changing a bit from 1 to 0. Thus, power traces with greater power consumption will be placed in one bucket and power traces with lesser power consumption will be placed in the other.

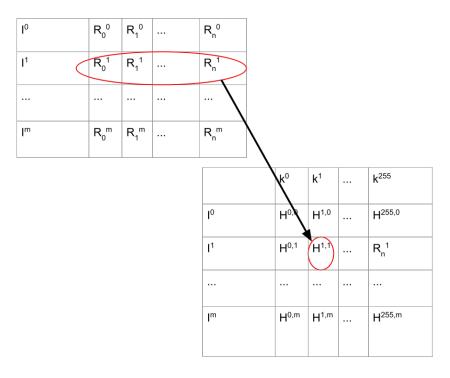

An example of DPA is shown in figure 1.6. The adversary begins by running an encryption algorithm a number of times using a hypothetical key guess [87]. Next, they collect power traces for a bit in the algorithm's execution that is directly dependent on a subset of the secret key(subkey). After this, they divide the traces into 2 buckets based on the value of the bit dependent on the subkey. The adversary calculates the mean of each bucket and repeats this process using different values for the subkey. They determine which subkey is correct by finding which value results in the largest difference between means for its two buckets. The adversary repeats this process until they are able to recover all the bits of the secret key.

More recent DPA approaches take a multivariate approach by comparing multiple points on a trace to one another rather than choosing a single point [127]. This trend arose because previous approaches consider measurements of power consumption at different points in time to be independent from one another. This means that if the power consumption of point 1 changes,

**Figure 1.6.** Differential Power Analysis(DPA) example

there is no guarantee that the power consumption of point 2 will change. However, in the case of encryption, it is very possible for one point in an algorithm's execution to directly affect another point in the algorithm's execution. Therefore, it is possible for an adversary to acquire secret information by analyzing how different points in an algorithm change with respect to each other.

One way to launch a multivariate DPA attack is by developing a multivariate Gaussian distribution [127]. A Gaussian distribution is a way to determine the likelihood of a measurement being equal to specific value. If the measurements within a bucket are normally distributed, it is highly likely that a bucket assumes the correct value for a bit and if the measurements within a bucket are not normally distributed it is highly unlikely that the bucket assumes the correct value for a bit. Furthermore, if we consider multiple points in a trace, the variance of each individual

point and the variance between each 2 sets of points we are able to distinguish subkey guesses in the presence of greater noise. This is because there are more requirements a subkey guess must satisfy in order to achieve high likelihood value.

#### **Correlation Power Analysis**

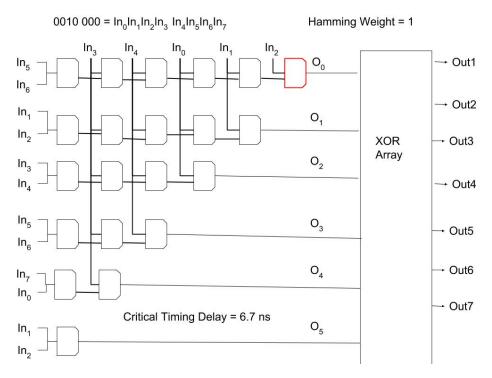

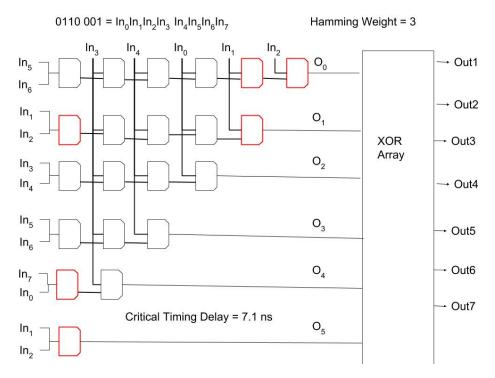

While DPA compares power traces to other power traces, Correlation Power Analysis (CPA) develops a power model for the implementation of a cryptographic algorithm [19] and compares power traces to the devloped model. The CPA power consumption model stems from the fact that the power consumption of the device should have a linear correlation with the Hamming Weight of a reference state dependent on a subkey key. The attacker is able to determine the subkey by observing which of their subkey guesses has the highest correlation to the power consumption model.

One way to calculate the correlation between a power model and the actual power consumption is by using the Pearson correlation coefficient equation [87]. The Pearson correlation coefficient equation operates by calculating whether there is a linear correlation between two sets of values. For example, if the Hamming Weight of a reference state increases as the measured power consumption increases, there will be a strong positive correlation between Hamming Weight and power consumption. The adversary determines which subkey is correct by finding which value results in the strongest correlation between Hamming Weight and power consumption.

#### **Template Power Analysis**

While DPA and CPA overcome noise by collecting more trace, Template Power Analysis(TPA) overcomes noise by profiling the power consumption of a device and comparing a few power traces to the profile [87]. The TPA power consumption model uses a large number of traces using different potential plaintexts and keys on a device identical to the device they intend to attack. Afterwards, the adversary collects a small number of power traces using the actual

key and determines which subkey guess is correct by determining whether an observed power consumption value is similar to an power consumption value from the profile

## 1.2.2 Electromagnetic Analysis Attacks

A number of devices generate electromagnetic(EM) radiation at unintended frequencies as a consequence of their internal operations [55]. This occurs because EM waves are generated from electrical currents changing over time and the frequency, amplitude and phase of these waves are dependent on how the electrical currents vary [42]. By analyzing these EM waves, an adversary is able to acquire information about the instructions that generated them. A number of EM attacks have been used to reveal the secret key in a variety of scenarios [55, 68, 114, 9, 33, 11, 24, 22, 21, 23, 20, 25, 46, 50, 52, 53, 54, 66, 69, 70, 71, 73, 79, 93, 98, 111, 115, 124, 133, 132, 136, 142, 141, 143, 149, 42, 43, 139, 41, 47, 63, 95, 126, 83, 147, 144, 39, 29, 112, 100, 102, 101, 103, 91, 84, 1, 148, 137, 91]

#### **Simple Electromagnetic Analysis (SEMA)**