# **Hardware Information Flow Tracking**

WEI HU, Northwestern Polytechnical University, China

ARMAITI ARDESHIRICHAM, University of California, San Diego, USA

RYAN KASTNER, University of California, San Diego, USA

Information flow tracking (IFT) is a fundamental computer security technique used to understand how information moves through a computing system. Hardware IFT techniques specifically target security vulnerabilities related to the design, verification, testing, manufacturing, and deployment of hardware circuits. Hardware IFT can detect unintentional design flaws, malicious circuit modifications, timing side channels, access control violations, and other insecure hardware behaviors. This article surveys the area of hardware IFT. We start with a discussion on the basics of IFT, whose foundations were introduced by Denning in the 1970s. Building upon this, we develop a taxonomy for hardware IFT. We use this to classify and differentiate hardware IFT tools and techniques. Finally, we discuss the challenges yet to be resolved. The survey shows that hardware IFT provides a powerful technique for identifying hardware security vulnerabilities as well as verifying and enforcing hardware security properties.

CCS Concepts: • Security and privacy → Logic and verification; Information flow control; Formal security models.

Additional Key Words and Phrases: Hardware security, information flow security, information flow tracking, security verification, formal method, survey

#### **ACM Reference Format:**

Wei Hu, Armaiti Ardeshiricham, and Ryan Kastner. 2020. Hardware Information Flow Tracking. ACM Comput. Surv. 0, 0, Article 00 (April 2020), 38 pages. https://doi.org/10.0000/0000000.0000000

## 1 INTRODUCTION

A core tenet of computer security is to maintain the confidentiality and integrity of the information being computed upon. Confidentiality ensures that information is only disclosed to authorized entities. Integrity maintains the accuracy and consistency of information – verifying that it is correct, complete, and not modified in any unauthorized manner. Understanding how information flows throughout a computing system is crucial to determine if that system operates securely with respect to confidentiality and integrity.

Information flow tracking (IFT) is a security technique that models how information propagates as a system computes. It labels data objects with a tag to denote security classes, which are assigned different meanings depending on the type of security property under analysis. IFT updates the tags as the data is computed upon, and verifies information flow properties by observing the state of the tags.

Information flow tracking can reason about the confidentiality and integrity properties. IFT verifies confidentiality by determining if secret information can ever be disclosed to an unclassified location. An example confidentiality property states that information related to a secret key should not leak outside a restricted memory space. IFT can also verify data integrity properties by not allowing untrusted entities to operate on trusted information. An example integrity property states that a user level program can never modify the system configuration data.

Authors' addresses: Wei Hu, Northwestern Polytechnical University, 127 Youyi Xi Lu, Xi'an, Shaanxi, 710072, China, weihu@nwpu.edu.cn; Armaiti Ardeshiricham, University of California, San Diego, 9500 Gilman Dr., La Jolla, CA, 92093, USA, aardeshi@ucsd.edu; Ryan Kastner, University of California, San Diego, 9500 Gilman Dr., La Jolla, CA, 92093, USA, kastner@ucsd.edu.

2020. Manuscript submitted to ACM

IFT has been used to enforce security properties across the computing system stack including operating systems [35, 78, 160], programming languages [126], distributed systems [104, 161], and cloud computing [6]. It can detect and prevent a wide range of software security issues including buffer overflow, memory corruptions, SQL injection, formatted string attack, cross-site scripting attacks, and malware [1, 36, 101, 108, 137]. IFT has been applied to verify the functional correctness and security of complex software systems like the *SeL4* secure OS kernel [74, 103]. More recently, hardware IFT techniques have been used to detect and assess security threats related to hardware design vulnerabilities [65, 135], insecure debug modes [15, 60, 123], timing channels [2, 4, 29, 64, 162], and hardware Trojans [44, 53, 107, 152]. A survey on security verification of hardware/software systems cited information flow analysis as the most commonly used technique for modeling and reasoning about security [26].

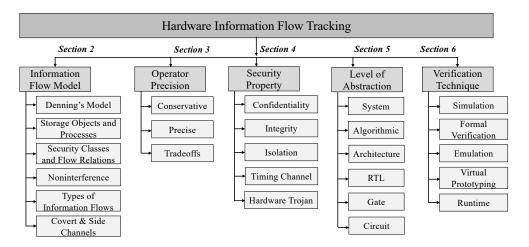

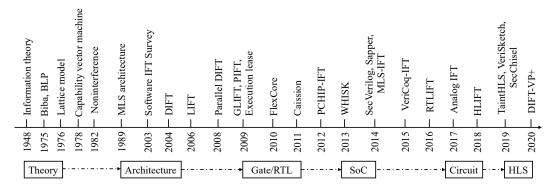

This article introduces a hardware IFT taxonomy, which is used to survey, classify, and compare hardware IFT techniques. We start by discussing the initial information flow model put forth by Denning [30, 31]. We identify the distinguishing characteristics of Denning's information flow model including the *security property* enforced, *level of abstraction*, *operator precision*, and *verification technique*. We use this to create a taxonomy to help compare and contrast the hardware IFT techniques. Figure 1 shows a taxonomy which consists of the following elements:

Fig. 1. A taxonomy for hardware information flow tracking. We start by describing the characteristics of an information flow model and define basic terminology. After that, we expand on different ways to classify the IFT techniques. The precision of class combining operator as well as the type of security property under consideration play an important role in defined the characteristics of the IFT technique. Another distinguishing characteristic is the abstraction level of the technique's information flow model. Finally, the IFT techniques enable different forms of verification, which provides another method of differentiation.

- Operator Precision: How does the class combining operator update security classes?

- Conservative: IFT operator uses a least upper bound.

- **Precise:** IFT operator considers the effect of data values.

- Tradeoffs: IFT operator performs tradeoffs between precision and computational complexity.

- **Security Property:** What types of security properties are supported?

- Confidentiality: IFT technique prevents leakage of sensitive information.

- Integrity: IFT technique prohibits overwriting of trusted data by an untrusted entitites.

- Isolation: IFT technique prevents communication between two entities of different trust.

- Timing channel: IFT technique captures information flows through a timing channel.

- Hardware Trojan: IFT technique detects malicious design modifications.

- Level of Abstraction: What is the level of abstraction of the information flow model?

- **System:** IFT technique considers system level flows.

- **Algorithmic:** IFT technique is deployed during high-level synthesis.

- Architecture: IFT technique is deployed at the instruction set architecture (ISA) level.

- RTL: IFT technique targets register transfer level (RTL) design.

- Gate: IFT technique considers a gate-level netlist.

- Circuit: IFT technique targets analog and mixed-signal hardware designs.

- Verification Technique: Which verification techniques are supported?

- **Simulation**: IFT technique uses simulation tools to determine information flows.

- Formal verification: IFT technique employs formal methods to verify security properties.

- **Emulation:** IFT technique allows for hardware emulation of information flow behaviors.

- Virtual prototyping: IFT technique creates a software version of hardware to measure information flows.

- Runtime: IFT technique can dynamically track information flows during runtime.

We use this taxonomy to classify and describe different hardware IFT techniques. This helps us discuss the relative advantages, weaknesses, and drawbacks of these techniques. We attempt to draw a clear picture of the past and future of hardware IFT research with a focus on its capability for developing new hardware security tools.

The remainder of this article is organized as follows. In Section 2, we discuss the core concepts of information flow, covering the fundamental elements in Denning's information flow model [31], the classical noninterference model [42], the different types of flow relations as well as basics of covert and side channels. Section 3 formalizes the concept of class combining operator precision and discusses IFT precision and computational complexity tradeoffs. In Section 4, we describe the different types of security properties that can be modeled and enforced under the information flow framework. Sections 5 reviews existing hardware IFT techniques from the perspective of the level of abstraction where they are deployed while Section 6 elaborates on the various mechanisms for performing information flow security verification. We discuss potential research vectors and challenges in Section 7 and conclude the article in Section 8.

## 2 INFORMATION FLOW

Information flow tracking (or information flow control) verifies that no unauthorized flow of information is possible. IFT techniques work by labeling storage objects with a security class, tracking those labels as their data is computed upon, and enforcing information flow policies to understand, verify, and/or control the movement of information in the system. Simple examples of policies include: 1) confidential information should never leak to an unclassified location and 2) untrusted information should never overwrite a trusted memory component.

Denning developed the earliest models for *information flow* [30, 31] that enables one to define the allowable flows of information between storage objects  $\mathcal N$  using security classes  $\mathcal S\mathcal C$  and flow relations  $\to$ . Processes  $\mathcal P$  operate on those storage objects. And a class combining operator  $\oplus$  provides a relationship between security classes. We use Denning's information flow model to discuss and compare different hardware IFT techniques.

An information flow model  $\mathcal{FM}$  is defined by  $\mathcal{FM} = \langle \mathcal{N}, \mathcal{P}, \mathcal{SC}, \oplus, \rightarrow \rangle$  where:

•  $\mathcal{N} = \{a, b, \dots\}$  is a set of *storage objects*. Elements of  $\mathcal{N}$  can vary depending on the level of abstraction under consideration, e.g., files, segments, registers, and flip-flops.

•  $\mathcal{P} = \{p, q, \dots\}$  is a set of *processes* where information flows through, e.g., functions, arithmetic operations and Boolean gates.

- $SC = \{A, B, \dots\}$  is a set of *security classes* corresponding the security classification of data objects, e.g., secret and unclassified. The security class associated with the information stored in an object a can either be bound statically or updated dynamically with the propagation of information. These are also commonly called *labels* or *tags*.

- The class combining operator ⊕ takes a pair of security classes and calculates the resulting security class, i.e.,

SC × SC → SC.

- A flow relation  $\rightarrow$  is defined on a pair of security classes. It is a "can flow" relation on SC, i.e.,  $\rightarrow \subseteq SC \times SC$ . Information flows from class A to class B whenever information associated with A could affect the value of data object associated with B. In other words, there exists a situation where changing the value of object associated with A leads to a change in the value of object associated with A. We write  $A \rightarrow B$  if and only if information in class A is allowed to flow to class B.

We attempt to adopt this classic notation as much as possible throughout this article. Our goal is to classify the work in hardware IFT using this notation so that it can provide a common language to compare and contrast the different techniques and methodologies. In the following subsections, we elaborate on the elements of this information flow model. Section 2.1 describes *storage objects* and *processes* from a hardware viewpoint. Section 2.2 discusses relevant information related to the *flow relations* and *security classes*. Section 2.3 introduces the idea of *noninterference*. Section 2.4 categorizes and illustrates the different types of *information flow relations*. Section 2.5 covers the basics of *covert* and *side channels*.

## 2.1 Storage Objects and Processes

An *object* is a container of information and a *process* describes computations performed upon those objects. Storage objects and processes vary depending on the security policies and level of abstraction. The initial work by Denning [30, 31] largely considered the security of software processes or programs. Much of it focused on security at the operating system level, and thus objects were things like files, directories, and users. Hardware storage objects are constructs defined in hardware description languages (HDLs) and their corresponding logical representations and physical implementations.

In hardware design, storage objects are defined using HDL types that can take or store values, e.g., input and output ports, internal wires and signals, registers, flip-flops, and memory blocks. It is often convenient to consider objects as any stateful elements in the hardware, i.e., to ignore wires and signals and focus on registers, flip-flops, and memory blocks. These objects are operated upon by processes  $\mathcal{P}$  that can be defined as register transfer operations, finite state machine (FSM) actions, combinational functions, and other common hardware models of computation.

Unfortunately, "process" is an overloaded term since process is a defined keyword in VHDL which denotes a set of sequential statements. The security notion of a process ( $\mathcal{P}$ ) covers a much broader scope; it refers to any arithmetic, logical or analog hardware component that operates on input data objects and produces a resulting object. Examples of hardware process  $\mathcal{P}$  include arithmetic, logical, and circuit-level operations.

#### 2.2 Security Classes and Flow Relations

Information flow policies define allowable relationships between data objects. To do this, IFT associates every object with a security class, i.e., gives objects a *security label* or *security tag*. Objects define the functional state of the system; their security labels determine the system security state.

The flow relation operator  $\rightarrow$  defines an allowable flow of information on two security classes.  $SC = \{A, B\}, A \rightarrow B$  states that information from security class A is allowed to flow to security class B. We can also denote the lack of an information flow with the operator  $\rightarrow$ , e.g.,  $B \rightarrow A$  states that information in security class B should never flow to security class A.

Security practitioners often use a *lattice* to describe flow relations. For example, Denning defined information flow policies as a finite lattice [31]. A lattice is in the form of  $\mathcal{L} = \{\mathcal{E}, \sqsubseteq\}$ , where  $\mathcal{E}$  is the set of elements and  $\sqsubseteq$  is a partial order relation defined on  $\mathcal{E}$ . The tuple  $\{\mathcal{E}, \sqsubseteq\}$  constitutes a *lattice* if there exists a *least upper bound* element and a *greatest lower bound* element for any  $A, B \in \mathcal{E}$  in the element set. The class combining operator  $\oplus$  is also a least upper bound operator in that for all  $A, B, C \in \mathcal{E}$ :

$$A \to A \oplus B$$

and  $B \to A \oplus B$

$A \to C$  and  $B \to C \implies A \oplus B \to C$  (1)

The greatest lower bound operator  $\odot$  is defined as  $A \odot B = \bigoplus LSet(A, B)$ , where  $LSet(A, B) = \{C \mid C \rightarrow A \text{ and } C \rightarrow B\}$  is the set of security classes from which information can flow to both A and B.

We usually consider lattices with finite number of elements. Let  $\mathcal{E} = \{A_1, A_2, \dots, A_n\}$ . The least upper bound (also called *maximum element*, denoted as high) and the greatest lower bound (also called *minimum element*, denoted as low) on the lattice are defined as follows:

$$\begin{aligned} & \text{high} = A_1 \oplus A_2 \oplus \cdots \oplus A_n \\ & \text{low} = A_1 \odot A_2 \odot \cdots \odot A_n \end{aligned} \tag{2}$$

An information flow policy/property can be modeled using a *security lattice*  $\mathcal{L} = \{SC, \sqsubseteq\}$ , where SC is a set of security classes and  $\sqsubseteq$  is the partial order defined on SC. Given any two security classes  $A, B \in SC$ , we say A is lower than B (or B is higher than A) when  $A \sqsubseteq B$ .

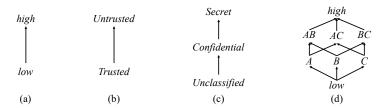

Fig. 2. Example security lattice structures. The lattice defines allowable information flows. Any operations that lead to an unallowable flow (e.g., allowing Untrusted information to flow to a Trusted data object or Confidential information to flow to an Unclassified data object) result in a security violation. Information flow is allowed to flow upward along the arrow in the security lattice; downward flows of information are not permitted.

Figure 2 provides four examples of lattices commonly used in modeling security. Figure 2 (a) shows the high and low security lattice that we mentioned earlier. Here, the security class set has two elements  $SC = \{\text{high, low}\}$ . The partial order (reflected by the arrow) defines allowable flows of information among different security classes, e.g., low  $\sqsubseteq$  high indicating that low information is allowed to flow to a high data object.

Figure 2 (a) to (c) are linear security lattices, where any two security classes are ordered or comparable. There are also more complex lattice structures with partial ordering. Figure 2 (d) gives an example of such non-linear security lattice, which contains non-comparable security classes, e.g., security classes A and B as well as A and BC. Information flow between security classes without partial order defined by the lattice should be prohibited.

In practice, most policies use a two-element lattice like in Fig. 2 (a). This allows the modeling of security properties related to confidentiality and integrity as  $low \sqsubseteq high$ . In cases where multi-level security needs to be enforced, often times we employ conservative label operators (e.g., the least upper bound or greatest lower bound operators) to determine the security class that the output of a process should take. More precise security class updating rules expand the two-level technique to account for the influence of the data values on security class operation [54, 55].

## 2.3 Noninterference

Noninterference is a strict multi-level security model proposed by Goguen and Meseguer [42]. It creates a model of information flow by modeling all system inputs, outputs, and state as either high or low. It states that any changes in high inputs shall not result in changes in low outputs. That is, low objects can learn nothing about high data. Another way of stating this is that a computer system produces the same low outputs for any set of low inputs regardless of the high inputs. That is, it is impossible to learn any information about the high values by changing the low inputs. Equivalently, the computer system responds exactly the same to any input sequence of low values regardless of the high values.

Noninterference provides a notion of strong, end-to-end security properties [128]. That is, it tracks the release and subsequent transmissions of the data to ensure that they adhere to the desired security properties. It extends the notion of access control [32, 80, 154], which strictly limits accesses to objects in the system. These lists enable restrictions on who can access an object; yet once it is released, its propagation is not restricted, and this information can be subsequently transmitted in an insecure manner.

Definitions of noninterference often rely on semantic models of program execution. Early work in this space includes Cohen's work using the notion of strong dependency [22, 23] and McLean's definition of noninterference using trace semantics [100]. Volpano *et al.* formalize Denning's lattice approach as a type system viewable as a form of noninterference [148]. Many follow-on works extend the expressiveness of the model and extend the typing system to handle concurrency, nondeterminism, synchronization and exceptions; for more information, see Sabelfield and Myers' excellent survey on language-based information flow security [126].

Much of this early work on noninterference was related to accessing user data and isolating programs running on shared computers. Thus, it largely dealt with files, resources, and users as objects and took a very "software" or operating system centric view. Regardless, the general notion of noninterference translates well to hardware. Perhaps the most straightforward example is the SecVerilog project [162], which employs the notion of noninterference using semantic models from Verilog. SecVerilog adds security labels to the Verilog language and extends previous security typing languages to hardware design. The challenge is accounting for all the eccentricities of the hardware models of computation, and in particular of vast use of concurrency. Regardless, the general idea that low objects should not be able to infer any information about the high objects still holds and can be translated to hardware.

A major challenge is that the number of objects in hardware is typically much larger than in software. Hardware objects could be comprised of the entire memory space, registers, and other low-level state – any stateful storage element could be considered. Of particular note is that objects can vary by the level of abstraction. For example, objects at the operating systems are files and users. ISA-level objects are visible programmer state, e.g., registers, memory, and Manuscript submitted to ACM

some program state (PC, status and configuration registers). Objects at the RTL would start to include intermediate registered values and state related to control flow. Objects at the gate level would likely denote every flip-flop which would include all registers (programmer visible or not) and the state of different controllers (i.e., finite state machine bits). Enforcing noninterference across all of these objects can be challenging. Yet, regardless of the number of objects, the notion of noninterference remains true – any information related to high objects should not flow to low objects.

## 2.4 Types of Information Flow Relations

While flow relations provide a way to specify security policies related to whether or not information is allowed to be transferred between objects, they do not strictly define the method to determine if there is a flow of information. There are many different ways in which information can be transmitted. Understanding the different types of information flow relations and how they manifest themselves in hardware is an important first step for precisely measuring all flows of information and further tightly enforcing the security policies.

Information can flow through functional (e.g., Boolean gates, arithmetic operators, transactions) and physical channels (e.g., power, electromagnetic, and thermal). A major difference between functional and physical flows lies in how information is encoded and transmitted. Functional flows encode information by using specified behavior of the hardware. The simplest example is directly writing data from one object to another. Physical information flows use some notion related to the physical process of performing the computation. This could be the time that an operation takes where examples include the time to receive data through a cache or compute some operation whose execution time depends on the data involved in the computation (e.g., modular exponentiation [77]). Additionally, any circuit switching activity results in power consumption, electromagnetic radiation, and thermal emission. Each of these can be used to infer what is being computed, and thus creates a flow of information.

In this article, we primarily focus on functional information flows, which traditionally have been categorized as *explicit* and *implicit*. In the following, we illustrate the difference between explicit and implicit flows. We also discuss a special type of implicit flow called *timing flow*, which usually leads to leakage of sensitive information.

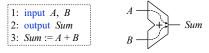

2.4.1 **Explicit Flow**. Explicit flow is associated with the direct movement of data. Thus, it is also called *data flow*. As shown in Fig. 3, information flows explicitly from the source operand(s) to the destination operand (from A and B to Sum in this example) when an expression sum := A + B is evaluated.

Fig. 3. A simple example of explicit flow. The data from A and B explicitly flow to Sum when the add operation is executed.

2.4.2 **Implicit Flow**. Implicit flow is a more subtle type of information flow that is caused by context dependent execution such as conditional operations. Here, information can flow between two objects even when there is no direct data assignment. Consider the example shown in Fig. 4 (a), which implements a simple if/else control structure.

It is clear that both A and B flow explicitly to Mux through the statements. The more challenging question is whether there is an information flow between Sel and Mux. There is obviously no direct explicit flow. However, it is possible to infer the value of Sel depending on what is written into Mux, i.e., whether Mux is assigned the value from A or B. Thus, there is an information flow, or more precisely an implicit information flow between Sel and Mux. Information Manuscript submitted to ACM

Fig. 4. A simple example of implicit flow. (a) The if/else hardware control structure causes a flow of information from Sel to Mux even though there is no direct assignment of the Sel data to Mux. As the design is synthesized to RTL (b) and gate level (c), the implicit flow becomes explicit as the multiplexer in (b) and the gates in (c) now denote an explicit flow between Sel and Mux.

flows implicitly from the conditional variable *Sel* to *Mux*, where how *Mux* will be updated depends on the value of *Sel*. It is important to understand that an implicit flow can occur even if there is no explicit data assignment.

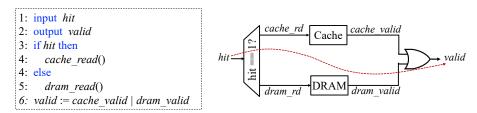

2.4.3 **Timing Flow**. A *timing flow* is a special type of implicit flow where information is flows through timing-related design behavior. Figure 5 shows a simple example of cache timing flow. The cache signal *hit* input affects the time at which the *valid* signal is asserted. It is not a functional flow because *valid* will eventually be asserted regardless of the value of *hit*. Yet, by observing the time at which *valid* is asserted, an attacker can infer the value of *hit*. Thus, *hit* flows to *valid* through a timing channel.

Fig. 5. A cache timing flow. The signal hit flows to the signal valid through a timing channel, i.e., an attacker can determine information about hit by observing when valid is asserted.

A more subtle case is that an information flow measurement can be a mix of functional and timing. Consider a RSA implementation through repeated square-and-multiply used in Kocher's timing attack [77]. There is functional flow from the key to ciphertext since the value of key directly affects the encryption result. However, there is also a timing flow to *cipher* in this implementation since the individual key bits determine the amount of time needed to encrypt a given message. It is possible to distinguish between timing flows from functional flows using hardware IFT [2, 113]. Manuscript submitted to ACM

#### 2.5 Covert and Side Channels

A covert channel is a transfer of information using an unintended source. The Orange Book classifies two types of covert channels - storage and timing channels [99]. The *storage covert channel* transmits information to a "storage location" (e.g., disk sectors) from parties in different security levels that are not allowed to communicate. The *timing covert channel* transmits information through the usage of system resources, which are observable by another process.

Lampson defined a covert channel as a channel "not intended for information transfer at all, such as the service program's effect on system load" [79]. Sabelfeld and Myers followed this notion and characterized covert channels as ways to transfer information within a computing system using mechanisms not intended to function as information channels. They classified covert channels to several categories, including implicit flows, termination channels, timing channels, probabilistic channels, resource exhaustion channels, and power channels [126]. Covert channels can be a security threat depending on what attackers can observe about the computing system, e.g., execution time, power consumption, resource usage and probability distribution of observable data.

By comparison, a side channel is a leakage of information through non-functional (often physical) characteristics, e.g., execution time, power consumption, EM radiation, and acoustic emissions. Kocher pioneered in developing side channel attacks to recover the cryptographic key from runtime and power trace measurements using statistical analysis [76, 77]. Meltdown [88], Spectre [75], and Foreshadow [13, 153] leverage architectural level security flaws to load kernel information into cache and then use timing channel attack to retrieve protected information. These side channels are caused by access to shared resources. There also can be a security threat in shared computing environments such as the cloud server [155].

An interesting consequence of modeling information flow at the hardware level, is that it provides cycle accurate timing information enabling timing channels (or lack thereof) to be modeled and formally verified using IFT [2, 4]. Section 4 describes this in more detail.

Covert and side channels often exploit similar phenomenon, e.g., timing, power consumption, and thermal radiation. A major difference between a covert and side channel is intent. A covert channel often times involves one party attempting to transfer information to another; a side channel is usually unintentional, but it often exploited as a vulnerability.

## 3 OPERATOR PRECISION

IFT techniques can use different class combining operators (or label propagation policies) to calculate the security class of the output upon input security labels. The type of operator employed can affect the precision of an IFT technique in measuring information flows and further the computational complexity to do the measurement. This section categorizes IFT techniques by operator precision and also discusses precision and complexity tradeoffs.

## 3.1 Precision of IFT

Precision is an attribute that reflects whether an IFT technique can accurately measure all (and only) existing information flows in hardware designs. Let O be an n-input function denoted as  $O = f(I_1, I_2, \dots, I_k, \dots, I_n)$ . A precise IFT technique indicates a flow from  $I_k$  to O if and only if the value of input  $I_k$  ( $1 \le k \le n$ ) has an effect on that of O, i.e., a change in the value of  $I_k$  will result in a change in O.

$$I_k \to O \Leftrightarrow f(I_1, I_2, \cdots, I_k, \cdots, I_n) \neq f(I_1, I_2, \cdots, I'_k, \cdots, I_n)$$

(3)

Precise IFT techniques can accurately model the information flow behaviors of hardware designs while imprecise ones can either indicate non-existent information flows (i.e., false positives) or miss actual information flows (i.e., false negatives). The false positives in information flow measurement correspond to information flow behaviors that would not actually happen. Most imprecise IFT techniques tend to introduce false positives, which are safe but may lead to conservative design decisions, i.e., a perfectly secure design may be verified as insecure. However, it should be noted that false negatives can arise due to incomplete analysis, e.g., when an information flow security property cannot be verified within reasonable amount of time and resource.

## 3.2 Imprecise IFT

Early hardware IFT techniques all tend to employ the conservative least upper bound operator in Denning's information flow framework to calculate the output security class and determine the flow of information [12, 137]. These techniques assume that information will always propagate from the inputs to outputs driven by them. In other words, information flows are independent of the functionality of the component and input conditions; the output will take a high label as long as any input is high. Let  $\mathcal{L}(I_1)$ ,  $\mathcal{L}(I_2)$ ,  $\cdots$ ,  $\mathcal{L}(I_n)$  be the security labels of the inputs  $I_1, I_2, \cdots, I_n$  respectively and  $\mathcal{L}(O)$  be the security label of output O. The conservative label propagation policy can be formalized as Equation (4), where the  $\oplus$  symbol represents the least upper bound operator. Imprecise IFT techniques employing this label propagation policy has the computational complexity of  $O(2^n)$ .

$$\mathcal{L}(O) = \mathcal{L}(I_1) \oplus \mathcal{L}(I_2) \oplus \cdots \oplus \mathcal{L}(I_n)$$

(4)

The label propagation policy shown in Equation (4) can be conservative for certain hardware components according to Equation (3). Consider the two-to-one multiplexer (MUX-2), whether an input could propagate to the output depends on the value of the select line.

Although imprecise IFT techniques can lead to conservative verification results, they usually allow a quick profile of potential information flow security vulnerabilities. This can be useful for identifying security violations that occur under rare conditions, e.g., a hardware Trojan that leaks information only when triggered [53]. However, the verification performance benefits that come at the cost of loss in precision may later be counteracted by additional efforts needed to exclude false alarms, e.g., a disabled debug port that had access to critical memory locations [52].

## 3.3 Precise IFT

Precise IFT techniques take into account both the functionality of a hardware component and the input values when determining flow relations. The label propagation policy can be formalized as a function of both the inputs and their labels as shown in Equation (5). Thus, the complexity of precise IFT techniques is  $O(2^{2n})$ .

$$\mathcal{L}(O) = f(I_1, I_2, \cdots, I_n, \mathcal{L}(I_1), \mathcal{L}(I_2), \cdots, \mathcal{L}(I_n))$$

(5)

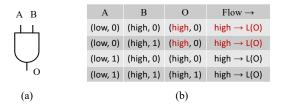

Gate level information flow tracking (GLIFT) [144] is the first well-established precise IFT technique. Figure 6 shows the difference in class combining operation with/without considering data values.

Figure 6 (b) and (c) show some partial flow relation and class combining operations without/with consideration of data values respectively. The entries in red text reveal the differences between these two rule sets. In Fig. 6 (b), the least upper bound operator is used for class combining and thus high information will always flow from *B* to *O*. However, data value can sometimes determine the output and prevent the flow of information from the other input. Take the Manuscript submitted to ACM

| A        | В         | О         | $Flow \rightarrow$ |  |

|----------|-----------|-----------|--------------------|--|

| (low, 0) | (high, 0) | (low, 0)  | $low \to L(O)$     |  |

| (low, 0) | (high, 1) | (low, 0)  | $low \to L(O)$     |  |

| (low, 1) | (high, 0) | (high, 0) | $high \to L(O)$    |  |

| (low, 1) | (high, 1) | (high, 1) | $high \to L(O)$    |  |

| (c)      |           |           |                    |  |

Fig. 6. Examples of flow relation and class combining operation. (a) Two-input AND gate. (b) Flow relation and class combining operation without considering data values. (c) Flow relation and class combining operation with consideration of data values.

second and third rows in Fig. 6 (c) for example. The (1ow, 0) input in A will dominate the output to be (1ow, 0). In such cases, the high information in input B does not have any effect on the output and thus cannot flow to O.

Oberg and Hu *et al.* have formalized precise IFT logic for Boolean gates under the notion of GLIFT [57, 111]. In a successive work, they performed a formal analysis on the complexity of the precise hardware IFT logic generation problem and revealed the impreciseness that can arise when tracking information flows in a constructive manner [58].

Ardeshiricham *et al.* proposed RTLIFT [3], a precise hardware IFT technique at the RTL. The major challenges are handling the complex conditional branch structures such as if-else, case and loop statements. However, RTLIFT allows more effective handling of timing flows modeled as conditional register updates controlled by tainted values [2].

Although RTLIFT has observed a magnitude of improvement over GLIFT in terms of verification performance and scalability, precise IFT can inevitably be expensive for large hardware designs since it is inherently an NP-complete problem [58]. Thus, it is desirable to derive practical IFT methods that can balance between the performance benefits and precision to achieve verification goals in acceptable amount of time and resource.

#### 3.4 Precision and Complexity Tradeoffs

Precision and complexity are two contradictory factors for evaluating hardware IFT techniques [52]. We have to tradeoff one for the other like we have done for area and performance in logic synthesis.

Switching circuit theories provide insightful explanations about the impreciseness of hardware IFT techniques. Oberg and Hu *et al.* have identified the root cause of false positives in IFT analysis as static logic hazards [57, 111]. They used a MUX-2 example to demonstrate how false positive will arise when there is either static-0 or static-1 logic hazard.

Hu *et al.* associate the source of impreciseness with internal variable correlations caused by reconvergent fanouts [58]. They also formally proved that precise hardware IFT logic generation is an NP-complete problem. To overcome the exponential scale complexity of the precise IFT logic generation problem, constructive as well as heuristic methods were proposed to create imprecise tracking logic in polynomial time at the cost of loss in precision.

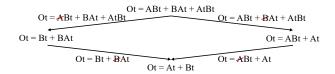

In [52], Hu *et al.* investigated the effect of logic synthesis optimizations on precision of IFT. This work reveals that the false positives of hardware IFT hide behind unreachable satisfiability don't care conditions in digital circuits. It provides an efficient approach to derive different version of hardware IFT logic with variable precision and complexity for Boolean gates. The observation is that precise IFT logic more accurately measures information flows because it considers the value of variables in label propagation. We would move towards the less precise by gradually ignoring the inputs to relax precision. Figure 7 illustrate this process using the two-input AND (AND-2) gate as an example, where A, B and O are the inputs and output of AND-2;  $A_t$ ,  $B_t$  and  $O_t$  are their security labels, respectively.

Fig. 7. Deriving simplified hardware IFT logic for AND-2.

At the top level, we have the most precise hardware IFT logic for AND-2. The second level shows three simplified versions of hardware IFT logic derived by setting one of the inputs to don't-care. By eliminating an additional input, we reach the least precise (but most simplified) hardware IFT logic for AND-2 at the bottom.

In [52], both graph and QBF-SAT based search techniques are proposed to gradually introduce false positives into hardware IFT logic to accelerate security verification and pinpoint security vulnerabilities. Becker *et al.* took a step further to quantitatively introduce a certain percentage of false positives into IFT logic with the assistance of QBF solvers, allowing a finer-grained tradeoff between precision and complexity [7].

## **4 SECURITY PROPERTIES**

gInformation flow properties are expressed as flow relations over objects. The property specifies how information stored in hardware objects can or can not flow to other objects. For example, a confidentiality property is specified by stating certain flows cannot occur (e.g., secret  $\rightarrow$  unclassified). An integrity property is also specified by restricting flows (e.g., untrusted  $\rightarrow$  trusted).

gInformation flow tracking properties are examples of *hyperproperties* since they express expected behaviors that require verification across multiple traces [21]. A *trace* is an execution of the hardware, e.g., a set of waveforms denoting the values of the hardware registers over time. An individual trace can be determined to satisfy or violate a *trace property*. Functional hardware verification techniques use trace properties, which are defined over sets of traces, e.g., a register should be set to '0' upon reset. While trace properties can encode functional properties, IFT properties require comparing the hardware's behavior with respect to more than one trace. Hyperproperties are defined on sets of sets of traces (also called systems) and thus more complex than trace properties.

To illustrate the relationship between hyperproperties and hardware IFT, consider an *integrity* property, which indicates that the behavior of trusted objects should remain intact with respect to values of untrusted objects. This policy compares the hardware behavior over multiple traces with differing values for untrusted data. Consequently, the integrity policy cannot be represented as a trace property. However, integrity can be represented as a hyperproperty that considers multiple traces which are identical except for the value of the untrusted data. To preserve integrity, the system is expected to act identically (in terms of the trusted objects) across all the traces assuming they start from equivalent initial states. Using formal methods, this hyperproperty can be verified for all possible values of untrusted data components to provide a formal proof of integrity in all possible executions. gOr one could verify it in simulation or emulation by insuring that the security label never reach an undesired state. This likely will not provide total coverage, but typically scales better than formal verification techniques.

gHardware IFT tools model movement of information through the hardware using labels that store security relevant information. The labels indicate whether objects are trusted or untrusted, confidential or public, contains timing variation or not, etc. The property defines the initial conditions on the labels and a set of conditions for how the labels can or can not change during execution. For an integrity property, IFT uses labels to indicate if objects are trusted or not. Manuscript submitted to ACM

Objects which carry untrusted values are initialized to have a *high* label while other objects have a *low* label by default. To ensure integrity, the property states that the system compute in a manner that maintains the *low* labels for the objects which are assumed to be trusted throughout execution. Maintaining a *low* label in this scenario demonstrates that untrusted values have not influenced the trusted components.

In this section, we show how different security policies can be modeled from the perspective of information flow and provide example hardware IFT properties. We describe the properties as an assertion-based IFT property language [49]. Assertion-based verification is commonly used for functional hardware verification [40], and thus should be familiar with hardware designers. Additionally, commercial IFT hardware tools have adopted assertion-based verification for IFT properties [97, 98]. Assertion-based IFT verification works by initially setting labels in the system (through *assume* statements) and verifying that these labels do or do not propagate to some other object (through *assert* statements). We consider an information flow model where relevant hardware components are extended with a security label, and a two level lattice  $low \sqsubseteq high$  shown in Fig. 2 (a). We use the System Verilog Assertion (SVA) language to specify these properties.

## 4.1 Confidentiality

Confidentiality properties ensure that any information related to sensitive objects (labeled as high) never flows to an unclassified object (using a low label). For instance, in a cryptographic core the secret key should not flow to a point that is publicly observable. Confidentiality properties are written to protect secret assets in a given design. This is done by marking the secret assets or inputs with a high security label and monitoring the label of public ports and storage units. To preserve confidentiality, all public ports and storage units should maintain a low label throughout execution. Examples of confidentiality properties for various hardware designs such as crypto cores and arithmetic units are shown in the first four rows of Table 1. Here we wish to verify that sensitive/secret objects do not affect publicly viewable objects. To do this, we set the sensitive objects labels as high using the assume statement, and assert that the publicly viewable objects remain low.

Formal Representation Benchmark Synopsis (Confidentiality) Acknowledgement signal is not driven from sensitive requests assume (req[i] == high); assert (ack[j] == low) assume (mode[i] == high); assert (grant[j] == low) Scheduler (Confidentiality) Grant signal is not driven from sensitive modes Crypto Core (Confidentiality) Ready signal is not driven from secret inputs assume (key == high & plain\_text == high); assert (ready = assume (operand1 == high & operand2 == high); assert (ready == low)

assume (user\_inp == high);

assert (key == low)

assume (user\_inp == high); Floating Point Unit (Confidentiality) Ready signal is not driven from the inputs Crypto Core (Integrity) Key register is not modified by public inputs assert (debug\_en == low)

assume (user\_ inp == high)

assert (PC == low & private\_mem == low

assume (user[i] == high); Debug Unit (Integrity) Debug flag is not modified by public inputs Processor (Integrity) PC, private memory and control flow conditions are not modified by public inputs assert (asset[j] == low)

assume (req[j] == high); assert (ack[j] == low)

assume (req[j] == high); assert (ack[i] == low)

assume (mem[i] == high); assert (mem[j] == low) Access Control (Integrity) Unauthorized users cannot access protected units (Isolation) Accesses to different cores on an SoC are isolated (Isolation) Memory locations are isolated Memory assume (mem[j] == high); assert (mem[i] == low)

Table 1. Examples of hardware IFT properties related to confidentiality, integrity, and isolation.

## 4.2 Integrity

Integrity is the dual of confidentiality - here we mark untrusted hardware resources with a high label and verify that they do not affect critical components with low labels. For example, in a processor the program counter (PC) should not be overwritten by data from an unprotected network.

Integrity properties can be specified for any design where certain memory locations, registers, or flags should be protected against unauthorized access. This is modeled by marking public access such as user or network input with a high label and constraining the sensitive variables to maintain a low security label. Table 1 shows four integrity properties written for crypto cores, debug units, processors, and access control units.

#### 4.3 Isolation

Isolation can also be enforced as an information flow security property. Isolation states that there should never be information exchange between two components with different trust levels. For example, in SoC designs, trusted IP cores sitting in the secure world with low labels should be separated from those which are untrusted and are in the insecure domain with high labels. It should be noted that isolation is a two-way property as shown in the examples of Table 1.

## 4.4 Timing Channel

Information flow models can be used to capture timing side-channels in hardware designs. These properties assess whether sensitive information can be retrieved by measuring the computation time. To precisely capture timing flows, the information flow model needs to distinguish between logical and timing flows. Take as example a floating point division unit expected to run in constant time independent of the value of the operands. In this case, logical flow exists from the data inputs (i.e., the divider and dividend) to the data outputs (i.e., quotient and remainder) since the outputs are computed from the inputs. However, whether or not there is timing flow from the inputs to the outputs (i.e., if the arithmetic unit runs in constant time or not) depends on the implementation of the floating point unit.

Table 2 summarizes the properties used in [2, 4] to verify timing side channel in different hardware designs. Here, we assume an IFT model where the flow relation tracks timing-based information flows (denoted by *time*), e.g. as described in Clepsydra [2]. To verify timing leakage, the assertions are written over these "*time*" labels.

| Benchmark             | Synopsis                              | Formal Representation                                             |

|-----------------------|---------------------------------------|-------------------------------------------------------------------|

|                       |                                       | assume (dividend == high & divisor == high);                      |

| Sequential Divider    | Result is ready in constant time      | assert (quotient $==_{time}$ low & remainder $==_{time}$ low)     |

|                       |                                       | assume (dividend == high & divisor == high);                      |

| Sequential Multiplier | Result is ready in constant time      | assert (quotient $==_{time}$ low & remainder $==_{time}$ low)     |

| Cache                 | Data is available in constant time    | assume (index[i] == high ); assert (data[j] == $_{time}$ low)     |

| SoC Arbiter           | Requests are granted in constant time | assume (req[i] == high ); assert (ack[j] == <sub>time</sub> low ) |

|                       |                                       | assume (thread_active[i] == high );                               |

| Thread Scheduler      | Scheduling is done in constant time   | assert (thread_grant[j] == <sub>time</sub> low )                  |

|                       |                                       | assume (key == high & plain_text == high);                        |

| AES Cipher            | Cipher text is ready in constant time | assert (cipher_text == <sub>time</sub> low)                       |

|                       |                                       | assume (key == high & plain_text == high);                        |

| RSA Cipher            | Cipher text is ready in constant time | assert (cipher_text == <sub>time</sub> low)                       |

Table 2. Summary of properties used for detecting timing side channes.l

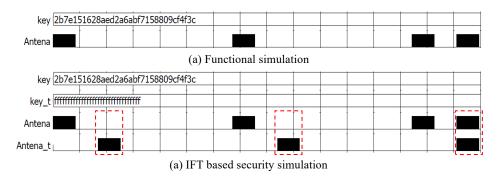

#### 4.5 Hardware Trojan

Information flow tracking can be used to detect certain types of hardware Trojans that leak sensitive information by inserting malicious information channels in the design. For example, Trust-HUB benchmarks [127] include examples of Trojans added to crypto cores using a small circuitry that transfers the secret key to a public output under certain conditions. This class of hardware Trojans can be detected using a property that observes information flow from Manuscript submitted to ACM

sensitive data (e.g., the secret key) to the public ports. Table 3 summarizes the properties for detecting information leakage by gate level information flow tracking in the Trust-HUB [127] benchmarks as used by Hu et. al. [53].

| Benchmark | Synopsis                            | Formal Representation        |

|-----------|-------------------------------------|------------------------------|

|           |                                     | assume (key == high);        |

| AES-T100  | Key does not flow to Antena         | assert (Antena == low)       |

|           |                                     | assume (key == high);        |

| AES-T400  | Key does not flow to shift register | assert (TSC-SHIFTReg == low) |

|           |                                     | assume (key == high);        |

| AES-T1100 | Key does not flow to capacitance    | assert (capacitance == low)  |

|           |                                     | assume (key == high);        |

| RSA-T200  | Key does not flow to count          | assert (count == low)        |

Table 3. Summary of properties used for detecting hardware Trojans

gThe Common Weakness Enumeration (CWE) is a community-developed list of software and hardware weakness types [96]. The hardware CWE list started in 2019 and includes a large number of enumerations that can be modeled using IFT properties. This includes most of the CWE categories including CWE-1195: Manufacturing and Life Cycle Management Concerns, CWE-1196: Security Flow Issues, CWE-1197: Integration Issues, CSE-1198: Privilege Separation and Access Control Issues, CWE-1199: General Circuit and Logic Concerns, CWE-1201: Core and Compute Issues, CWE-1202: Memory and Storage Issues, CWE-1205 Security Primitives and Cryptography Issues, CWE-1207: Debug and Test Problems, and CWE-1208: Cross-Cutting Problems. Many of these weaknesses can be modeled as IFT properties discussed in this section. The IFT based security verification tool *Radix* [97, 98] claims support of over 80% of the hardware CWEs.

## 5 LEVEL OF ABSTRACTION

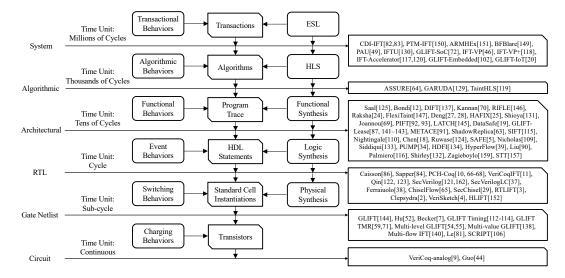

Hardware designs are translated through many levels of abstraction before implementation. Each abstraction level has different capability and accuracy in describing hardware behaviors, which in turn allow verifying of different types of security properties. For example, timing properties require cycle accurate precision which is only possible at the RTL and below. In the following, we categorize Hardware IFT techniques according to the abstraction level where they are developed and deployed, ranging from system, to RTL, and all the way down to Boolean gates and the circuits [3, 9, 39, 54, 67, 119, 129, 132, 137, 144, 157, 162].

Figure 8 shows some hardware design abstractions and the IFT tools at these different levels of abstraction. A question that would arise naturally is when and where to deploy hardware IFT? It is important to choose the right abstraction for the job [85]. At higher levels (e.g., system and algorithmic), the models abstract away significant amount of design details, which can lead to better verification performance and scalability. In addition, we can detect potential security vulnerabilities earlier in the design process and fix them at much lower cost. However, we usually need to make conservative assumptions about the hardware behaviors due to the lack of implementation details at such an early design phase. The architectural level has enough design information for verifying the security related interference between hardware and software as well as firmware. However, it is a non-trivial task to account for explicit flows and timing channels at this level. As we move to RTL, the model is cycle accurate and can capture timing information flows. However, the complex HDL syntax features (i.e., conditional branch statements) renders automatic IFT logic generation a complicated process. At the gate level, the complex syntax structures are simplified to Boolean gates and all information flows explicitly, significantly lowering the effort for IFT logic formalization. However, it is well-known that gate level simulation and verification is typically one or two orders of magnitude slower than doing the same job

Fig. 8. Hardware IFT techniques at different levels of abstraction.

at the RTL [8]. However, gate level and circuit level IFT techniques are still essential complements to higher level IFT methods. Some designs may come in the form of synthesized or layout netlist or we may want to understand if security properties still hold after logic synthesis and technology mapping.

### 5.1 System Level

A number of approaches explore hardware extension for dynamic information flow tracking (DIFT) to perform system level verification [20, 48, 72, 82, 83, 117, 130, 149, 151]. Some techniques use loosely-coupled processor or dedicated hardware to perform IFT at runtime while others employ IFT to verify system security during design time.

5.1.1 IFT Through Co-processing Unit. Lee et al. use CDI (Core Debug Interface) to fetch meta data [82, 83]. The ARM CoreSight ETM (Event Trace Macrocell) trace component is used to collect information for each CPU instruction. This trace component is later updated to CoreSight PTM (Program Trace Macrocell), which provides information only on instructions that modify the PC. Wahab et al. use this new debug feature in ARMv7 processor to retrieve details on instructions committed by the CPU to perform DIFT. A DIFT coprocessor is implemented in the program logic of Xilinx Zynq device [150] for tag processing. ARMHEx [151] is a DIFT solution leveraging the CoreSight PTM debug component. Static analysis and instrumentation are employed to retrieve the missing information resulting from the update. ARMHEx also considers the security of the DIFT unit by using ARM Trust-Zone to protect it. A successive work develops a more adaptive information flow monitor called BFBlare, which supports multi-thread, virtual tag memory, floating point and Linux kernel features [149].

Heo et~al. propose an application specific instruction set processor (ASIP) architecture for system level programmable dynamic program analysis [48]. The proposed approach is implemented as a hardware engine called program analysis unit (PAU), whose key components are the tag processing core and the main controller. The main controller communicates the execution traces with the host processor through the system bus. The tag processing core is an application specific instruction set architecture for management of tags.

Shin *et al.* proposed the implicit flow tracking unit (*IFTU*), an external hardware module connected to the host processor through system bus. In IFTU, for a conditional branch, the taint tag of data used for branch condition checking is first propagated to the program counter. Then, for the instructions after the conditional branch, the taint tag of the program counter is propagated to the destinations where the values are affected by the branch result. IFTU can detect more recent advanced attacks that exploited implicit flows at reasonable area costs [130].

5.1.2 IFT for Verifying and Enforcing SoC Security. Kastner et al. use IFT to prevent secret information from leaking (for confidentiality), and untrusted data from being used in the making of critical decisions (for integrity) in SoC systems using untrusted IPs [72]. They use a gate level information flow model but use it to verify system level properties.

Hassan *et al.* and Pieper *et al.* propose an approach for SoC security validation through Virtual Prototypes (VP) modeled using SystemC TLM 2.0 [46, 118]. They employ static information flow analysis to verify the *no flow* security property and detect potential security breaches such as data leakage and untrusted access. However, information flow is determined by static path search between the source and sink points, which can lead to conservative verification results.

Piccolboni *et al.* add support of DIFT to loosely coupled accelerators in heterogeneous SoCs, which are vulnerable to attacks [117]. It is inspired by two earlier works [119, 120] on DIFT targeting such accelerators. A standalone shell circuit is added for interacting with the accelerator, e.g., loading, propagating and storing tags.

5.1.3 IFT for Enforcing Embedded System Security. In [102], a bottom-up approach is proposed for enforcing information flow security in embedded systems. The paper implements bit-tight information flow control from the level of Boolean gates. It then exposes this information flow measurement capability to higher abstraction levels in the system stack ranging from architecture and all the way up to secure application to enforce security properties.

Cherupalli *et al.* propose a fine-grained IFT technique for enforcing information flow security for IoT systems [20]. They introduce application specific GLIFT [144] for IoT systems. The paper builds a gate-level symbolic analysis framework that leverages the knowledge of the target application to efficiently identify the potential information flow security vulnerabilities. It designs a software tool that takes as inputs the gate level netlist of the processor, the original binary of a given application and information flow policies of interest. The tool performs symbolic gate level simulation of the application binary on the netlist to determine if there is any information flow security policy violation and identify the offending instructions.

## 5.2 Algorithmic Level

Some recent works synthesize DIFT enhanced hardware accelerators from high-level specification [64, 119, 129].

ASSURE [64] is a security-constrained high-level synthesis (HLS) framework that automatically synthesizes verifiably secure hardware accelerators from high-level descriptions under user-defined security policies and constraints. ASSURE extends the LegUp HLS framework [17] to perform IFT. It generates an additional enforcement FSM to manage public I/O accesses separately in a way that all secret-conditioned branches are balanced by applying additional latency constraints. Other operations that do not affect timing of the public outputs are controlled by the main FSM. As a result, the public outputs have constant latency.

GARUDA [129] is a high-level security policy language and a compiler to compile security policies described in GARUDA to Verilog modules. It enables the modular construction and composition of runtime hardware monitors for securing a variety of security policies, including fault isolation, secure control flow, and DIFT via taint checking. The high-level security policies described in GARUDA are first converted into a policy intermediate representation (IR) and then compiled to Verilog code using the extraction feature of the Coq theorem prover.

TaintHLS [119] is an HLS methodology to automatically generate DIFT-enabled accelerators from high-level specification. TaintHLS creates a microarchitecture to support baseline operations and a shadow microarchitecture for intrinsic DIFT support in hardware accelerators. The DIFT-enabled accelerators have negligible performance overhead while adding no more than 30% hardware. These accelerators achieve the same value tags and identical number of false positives/negatives as compared to software IFT implementation.

#### 5.3 Architecture Level

5.3.1 Capability Vector Architecture. Architectural level hardware IFT research dates back to as early as Denning's information flow theoretic framework. In 1978, Saal and Gat from IBM proposed a *capability vector machine* to enforce access and information flow control [125]. The machine used a capability vector to describe information flow policy. For example, an instruction moving data from A to B required the capability vectors <(A, READ) and (B, WRITE)>. An instruction would be allowed to execute when its implied capability vector existed otherwise the movement of information should be prohibited.

Bondi and Branstad designed an architecture for fine-grained secure computing [12]. The architecture's operands are 2-tuples, consisting of a data object and an associated security tag. A dedicated subprocessor and tag memory are added to perform security tag manipulation in parallel to the data path. The coupled subprocessors enforce multi-level security (MLS) access control and information flow control. While such an architecture provides efficient security support, it is infeasible for modern processors with their large instruction set.

5.3.2 DIFT and Related Architectures. Dynamic information flow tracking (DIFT) is an architectural mechanism to protect programs against buffer overflow and format string attacks by identifying spurious information flows from untrusted I/O and restricting the usage of untrusted information [137]. Although DIFT employs conservative tracking rules, the performance overheads could be as high as 23% for certain benchmarks. To reduce the overheads, Kannan et al. propose to decouple DIFT with a co-processor [70]. The co-processor receives instruction tuples and loads tag information from tag memory/cache to perform security checks. The two processors synchronize on system calls. When a tag check fails, an exception would be generated and the execution results of the instruction and tag update would be rejected.

Runtime Information Flow Engine (*RIFLE*) enforces user-defined information flow security policies [146]. In RIFLE, program binaries are translated from a conventional ISA to an information flow secure ISA. The translated programs execute on hardware with IFT capability and interact with a security-enhanced operating system, which is responsible for enforcing the security policies. The authors also show that language-based information-flow systems are less secure than previously thought while architectural level IFT approaches can be at least as powerful as language-based information-flow systems.

Raksha is an architecture that combines both hardware and software DIFT mechanisms [24]. Hardware manages security tags at low performance overhead for user code, OS code, and data that crosses multiple processes while software performs security checks and handles exceptions. Raksha supports a flexible and programmable mechanism for specifying security policies, allowing multiple concurrently active security policies to deal with a wide range of attacks. It enables security exceptions that run at the same privilege level and address space as the protected program. This allows the integration of the hardware security mechanisms with software analyses, without incurring the performance overhead of switching to the operating system.

FlexiTaint [147] is another hardware accelerator for DIFT with support of flexible and configurable taint propagation rules. It extends the processor pipeline and implements taint-related logic for tag processing. Tags are stored as a packed array in virtual memory; a taint propagation cache tagged by operation type and input-operand taints to improve performance. Reported results showed that FlexiTaint incurred negligible performance overheads even when simultaneously supporting two different taint propagation policies.

In [27, 28], Deng *et al.* implement DIFT using a soft-core processor. The CPU pipeline is modified in order to allow the processing core to forward its execution trace for tag processing. In [25], executable binary is instrumented to extract the required information for DIFT. However, it causes up to 86% performance overhead.

Shioya *et al.* and Joannou *et al.* tried to reduce the memory overhead of DIFT techniques by exploiting tag memory access characteristics, e.g., non-uniformity, locality, and cache behavior. They propose to use multi-level table, cache structures and memory access optimizations to accelerate tag memory access [69, 131]. Another attempt to optimize taint label manipulation is to separate trusted and untrusted data objects into different pages, which prevents the overhead for storing and loading taint labels [92, 93].

Locality-Aware Taint CHecker (*LATCH*) is an architecture for optimizing DIFT [145]. The key observation is that that DIFT exhibit strong temporal locality, with typical applications manipulating sensitive data during limited phases of computation. This property allows LATCH to invoke precise, computationally intensive tracking logic only during the execution involves sensitive data otherwise perform lightweight, coarse-grained checks to reduce performance overheads. The authors design and implement three different DIFT systems that incorporate the LATCH model, i.e., S-LATCH for optimizing software-based DIFT on a single core, P-LATCH to optimize DIFT monitoring using a separate core and H-LATCH that targets hardware-based DIFT.

DataSafe is a software-hardware architecture that provides dynamic instantiations of secure data compartments (SDCs) [19]. The architecture enforces hardware monitoring of the information flows from the compartment using hardware policy tags associated with the data at runtime to prevent leakage of sensitive information. Security tags are derived from security policies associated with sensitive data and passed to the SDC for tag propagation. These tags would be checked when data were processed by unvetted applications.

5.3.3 Execution Lease Architectures. Tiwari et al. describe how a class of secure architectures can be constructed, from the gates up, to completely capture all information flows [141–143]. In [142], hardware IFT is applied to an FPGA device to create a micro-processor that implements bit-tight information flow control. The architecture design is a full implementation that is programmable and precise enough to track all flows of information and prevent untrusted data from flowing to critical memory locations such as the PC. Novel techniques are proposed to handle conditional branches, loops, loads and stores to prevent over tainting. A prototype processor is implemented on Altera Stratix II FPGA, where IFT logic adds about 70% resource overhead [143].

The execution lease is another IFT enhanced architecture [87, 141]. This lease architecture allows execution contexts to be tightly quarantined and their side effects to be tightly bounded. Information flow security properties such as isolation between trusted and untrusted execution contexts can be verified all the way down to the gate-level using the precise information flow measurement capability of IFT. However, all the leases have a fixed time bound, which does not support performance optimization micro-architecture features such as caches, pipelining, branch prediction or TLBs due to the timing variation they introduce. In addition, the lease architecture adds substantial design and performance overheads resulting from the additional information flow tracking logic.

To overcome the shortcomings of the lease architecture, in [143] a minimal but configurable architectural skeleton is crafted to operate along with a small piece of software, which together composes the minimal essential functionality through which information flow security properties can be verified all the way down to Boolean gates. Such strict core component is then used to create a hardware-software system that allows unbounded operation, inter-process communication, pipelining, I/O with traditional devices and other architectural level performance optimizations. This work also proposes a more scalable verification technique called star-Logic (\*-logic), which represents indeterministic values as the abstract value \* in order to verify all possible executions arising from unknown values in a single run.

5.3.4 IFT on Multi-core Architectures. Most architectural level IFT techniques discussed above used a dedicated coprocessor for tag processing. There are also works that distribute data processing and metadata processing to different cores in a single processor [18, 63, 91, 105, 110, 115, 124]. DIFT on multi-core processor can be a much more challenging task in that data processing and metadata processing are normally decoupled and in different orders. Maintaining metadata coherence is a fundamental problem for ensuring the correctness of DIFT in a multi-core environment. To address possible inconsistency, Santos *et al.* proposed *METACE* that included architectural enhancement in the memory management unit and leveraged cache coherence hardware protocol to enforce metadata coherence [91]. In addition, there is also performance penalty due to inter-process communication [105].

ShadowReplica [63] is another dynamic data flow tracking technique on multi-core processor. It uses a shadow thread and spare CPU cores to decouple execution and data flow tracking. The two processes communicate through a shared data structure. A major difference from previous approaches lies in that it introduces an off-line application analysis phase that utilizes both static and dynamic analysis methodologies to generate optimized code for decoupling execution and implementing DFT. This additional phase also minimizes the amount of information that is to be communicated between the two threads.

SMT-based IFT (SIFT) is a hardware IFT technique on SMT processors [115]. Taint propagation and policy checking are performed by a separate thread executed in spare context of an SMT processor. The instructions for the checking thread are generated in hardware using self-contained off-the-critical path logic at the commit stage of the pipeline. Instruction generation can be completed in one additional cycle at commit time. Experimental results using SPEC CPU 2006 benchmarks showed 4.5% area overhead, 20% overhead in performance and 23% additional power consumption, which is significantly lower than several software IFT implementations.

Another benefit of performing IFT on multi-core processors is the possibility of parallelizing DIFT in order to reduce the high performance overhead of sequential implementations. The major challenge lies in serial dependencies in DIFT, i.e., label propagation usually depends on resulting labels of prior operations. To accelerate DIFT, different optimizations are proposed to resolve and simplify such dependencies, e.g., preserving only operation that affect the taint status of critical points [110] and tracking the information flow only through unary operations [18, 124]. Afterwards, the parallelized DIFT instances are distributed to multiple cores for processing.

5.3.5 IFT on RISC-V Architectures. The SAFE project developed one of the earliest verified information flow secure architectures based on the RISC instruction set. A simple stack-and-pointer machine with "hard-wired" dynamic IFC was designed to provide IFT support to higher-level software. The instructions for implementing the IFT mechanism are formalized and verified using Coq [5]. More recent projects such as SSITH and AISS both aim to develop secure RISC-V architectures, where IFT is employed for verifying and enforcing security guarantees [109, 133].

Programmable Unit for Metadata Processing (*PUMP*) is an enhanced RISC processor architecture with ISA-level extension [34]. PUMP changes the pipeline to incorporate programmable tag propagation rule checking. PUMP performs Manuscript submitted to ACM

single-cycle common-case computation on metadata with support of the tag propagation rule cache. On every instruction, the tags of the inputs are used to determine if the operation is allowed, and if so to determine the tags for the results. A tag propagation rule cache miss will trigger the policy miss handler to determine if the instruction is allowed.

*HDFI* is a hardware-assisted solution for data flow isolation by extending memory words with single bit tags and the RISC-V ISA to perform tag checking [134]. The integrity level of a memory unit is determined by the last write operation to the unit. At memory read, a program would check if the tag is allowed by the security policy. HDFI enforces the Biba integrity and Bell-LaPadula confidentiality security models with <2% performance overhead.

HyperFlow [39] is another extended RISC-V architecture with security features for enforcing information flow control. The processor is designed and verified using a type enforced hardware design language ChiselFlow [65]. It supports rich configurable security policies described by complex lattice structures and controlled security class downgrading to allow inter-process communication and system calls. This new architecture also prevents timing channels by enforcing the security policy that the latency of an instruction should not depend on operand value or memory access from another process with a higher security type. A later work extends this architecture by also incorporating language-level IFC for securing the system architecture of secure autonomous vehicles [90].

Several other works build hardware IFT capability into RISC-V processor to provide hardware-assisted security [116, 132]. In [159], ISA based on IFC is designed to mitigate the gap between IFC hardware and software. This ISA is used to prove strong timing-sensitive security conditions about software, leveraging the IFC capabilities and guarantees provided by hardware.

5.3.6 IFT for Speculative Architecture. Speculative Taint Tracking (STT) [157] is a framework that executes and selectively forwards the results of speculative access instructions to younger instructions, as long as those younger instructions cannot form a covert channel. STT tracks the flow of results from access instructions in a manner similar to DIFT, until those results reach an instruction, or sequence of instructions, that may form a covert channel. It automatically "untaints" the result once the instruction that produces it becomes non-speculative to improve performance. The framework enforces a novel form of non-interference, with respect to all speculatively accessed data.

## 5.4 RTL

A large body of research work aims to develop hardware IFT techniques at the RTL or extend existing HDLs with IFT capability [2–4, 10, 11, 29, 37, 66–68, 84, 86, 162].