### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Templates and Patterns: Augmenting High-Level Synthesis for Domain-Specific Computing

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

by

Janarbek Matai

## Committee in charge:

Ryan Kastner, Chair Rajesh Gupta Ali Irturk Bhaskar D. Rao Michael B. Taylor

Copyright

Janarbek Matai, 2015

All rights reserved.

| The Dissertation of Janarbek Matai is approved and is acceptable in quality |

|-----------------------------------------------------------------------------|

| and form for publication on microfilm and electronically:                   |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

| Chair                                                                       |

| Chan                                                                        |

University of California, San Diego 2015

## **DEDICATION**

To mom and dad.

## **EPIGRAPH**

I wanted a perfect ending. Now I've learned, the hard way, that some poems don't rhyme, and some stories don't have a clear beginning, middle, and end. Life is about not knowing, having to change, taking the moment and making the best of it, without knowing what's going to happen next.

Gilda Radner

## TABLE OF CONTENTS

| Signatur            | re Page                                                                                                                                                                                                    | iii                                                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Dedicati            | ion                                                                                                                                                                                                        | iv                                                 |

| Epigrapl            | h                                                                                                                                                                                                          | V                                                  |

| Table of            | Contents                                                                                                                                                                                                   | vi                                                 |

| List of F           | Figures                                                                                                                                                                                                    | ix                                                 |

| List of T           | Tables                                                                                                                                                                                                     | XV                                                 |

| Acknow              | rledgements                                                                                                                                                                                                | XVi                                                |

| Vita                |                                                                                                                                                                                                            | xviii                                              |

| Abstract            | t of the Dissertation                                                                                                                                                                                      | XX                                                 |

| Introduc            | etion                                                                                                                                                                                                      | 1                                                  |

| Chapter 1.1 1.2 1.3 | 1 Background Introduction High-Level Synthesis 1.2.1 Scheduling Design with HLS 1.3.1 Vivado High-Level Synthesis                                                                                          | 77<br>79<br>10<br>15                               |

| 1.4<br>1.5          | HLS Hello World                                                                                                                                                                                            | 18                                                 |

| Chapter 2.1 2.2 2.3 | Introduction Wireless Channel Model Hardware Design and Optimization 2.3.1 Architecture 2.3.2 Baseline 2.3.3 Code Restructuring 2.3.4 Bit-Width Optimization 2.3.5 Pipelining/Unrolling/Partitioning (PUP) | 20<br>22<br>26<br>29<br>29<br>30<br>33<br>36<br>37 |

| 2.4                 | Results                                                                                                                                                                                                    | 38<br>38                                           |

| 2.5                 | Experimental Results                                                                                                                                                                                       | 40                                                 |

| 2.6                 | Discussion                                                                                                                                                                                                 | 44                                                 |

| 2.7     | Related Work                                           | 45  |

|---------|--------------------------------------------------------|-----|

| 2.8     | Conclusion                                             | 47  |

| Chaptar | 2. A Complete Feed Recognition System                  | 50  |

| Chapter | •                                                      | 50  |

| 3.1     | Introduction                                           |     |

| 3.2     | Face Recognition subsystem                             | 52  |

|         | 3.2.1 Architecture of the Face Recognition Subsystem   | 53  |

| 2.2     | 3.2.2 FPGA Implementation                              | 55  |

| 3.3     | Experimental Results                                   | 59  |

| 3.4     | Implementation of the Complete Face Recognition System | 60  |

| 3.5     | Conclusion                                             | 63  |

| Chapter | 4 Canonical Huffman Encoding                           | 64  |

| 4.1     | Introduction                                           | 64  |

| 4.2     | Canonical Huffman Encoding (CHE)                       | 66  |

| 4.3     | Hardware Implementations                               | 69  |

|         | 4.3.1 Radix Sort                                       | 72  |

|         | 4.3.2 Huffman Tree Creation                            | 74  |

|         | 4.3.3 Parallel Bit Lengths Calculation                 | 75  |

|         | 4.3.4 Canonization                                     | 76  |

|         | 4.3.5 Codeword Creation                                | 77  |

| 4.4     | Software Implementations                               | 79  |

| 4.5     | Experimental Results                                   | 80  |

| 1.5     | 4.5.1 Software Implementations                         | 80  |

|         | 4.5.2 Hardware Implementations                         | 82  |

|         | 4.5.3 Hardware and Software Comparison                 | 85  |

| 4.6     | Related Work                                           | 87  |

| 4.7     | Conclusion                                             | 88  |

| 1.7     | Conclusion                                             |     |

| Chapter |                                                        | 90  |

| 5.1     | Introduction                                           | 90  |

| 5.2     | Restructured Code                                      | 93  |

|         | 5.2.1 Prefix sum                                       | 94  |

|         | 5.2.2 Histogram                                        | 99  |

|         | 5.2.3 SpMV: Sparse Matrix Vector Multiplication        | 105 |

|         | 5.2.4 FFT                                              | 112 |

|         | 5.2.5 Huffman Tree Creation                            | 116 |

|         | 5.2.6 Matrix multiplication                            | 123 |

|         |                                                        | 127 |

|         | 5.2.8 Face Detection                                   | 131 |

| 5.3     | HLS User Study                                         | 139 |

|         | •                                                      | 139 |

|         |                                                        | 143 |

| 5.4      | Challenges                                                         | 147 |

|----------|--------------------------------------------------------------------|-----|

|          | 5.4.1 Restructured Code Generation: Instruction level              | 148 |

|          | 5.4.2 Restructured Code Generation: Task level                     | 148 |

|          | 5.4.3 Complex Application Design                                   | 150 |

| 5.5      | Conclusion                                                         | 151 |

| Chapter  | 6 Composable, Parameterizable Templates for High-Level Synthesis . | 153 |

| 6.1      | Introduction                                                       | 153 |

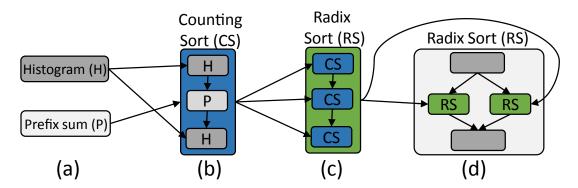

| 6.2      | Motivating Example: Sorting                                        | 155 |

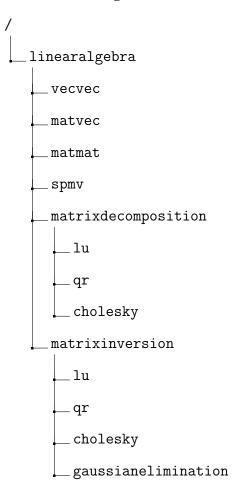

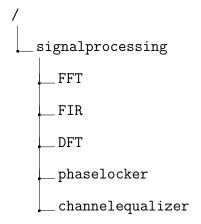

| 6.3      | Templates and Compositions                                         | 157 |

| 6.4      | Template Parameterization                                          | 162 |

|          | 6.4.1 Composition Algorithm                                        | 162 |

|          | 6.4.2 Parameterization                                             | 164 |

| 6.5      | Experimental Results                                               | 165 |

| 6.6      | Related Work                                                       | 171 |

| 6.7      | Conclusion                                                         | 173 |

| Chapter  | 7 Resolve: Automatic Generation of a Sorting Architecture          | 176 |

| 7.1      | Introduction                                                       | 176 |

| 7.2      | High-Level Synthesis Optimizations                                 | 177 |

| 7.3      | Hardware Sorting                                                   | 178 |

| 7.3      | 7.3.1 Sorting Primitives                                           | 180 |

|          | 7.3.2 Sorting Algorithms                                           | 183 |

| 7.4      | Sorting Architecture Generator                                     | 189 |

| 7.5      | Experimental Results                                               | 193 |

| 7.6      | Related work                                                       | 196 |

| 7.7      | Conclusion                                                         | 197 |

| Chapter  | 8 Future Research Directions                                       | 199 |

| 8.1      | End-to-End System Design                                           | 199 |

| 8.2      | Design Space Exploration                                           | 200 |

| 8.3      | Data Processing on an FPGA                                         | 201 |

| 0.0      | Machine Learning Acceleration                                      | 201 |

| Annendi  | ix A HLS Codes                                                     | 202 |

|          | Restructured Code                                                  | 202 |

|          | Streaming and Blocking Matrix Multiplication                       | 204 |

| Ribliogr | anhy                                                               | 208 |

## LIST OF FIGURES

| Figure 1.1. | High-Level Synthesis tool flow                                                                                                                       | 10 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2. | An example data flow graph                                                                                                                           | 11 |

| Figure 1.3. | ASAP Schedule                                                                                                                                        | 12 |

| Figure 1.4. | ALAP Schedule                                                                                                                                        | 13 |

| Figure 1.5. | Time frames for operations                                                                                                                           | 14 |

| Figure 1.6. | Distribution graphs for a multiplier and adder                                                                                                       | 14 |

| Figure 1.7. | HLS Hello World Hardware Architecture                                                                                                                | 20 |

| Figure 1.8. | Hardware architectures for hello world HLS code. a) Hardware architecture created by Listing 1.1 b) Hardware architecture that we want to create     | 20 |

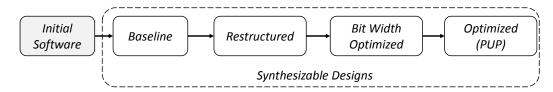

| Figure 2.1. | Overview of HLS design flow                                                                                                                          | 23 |

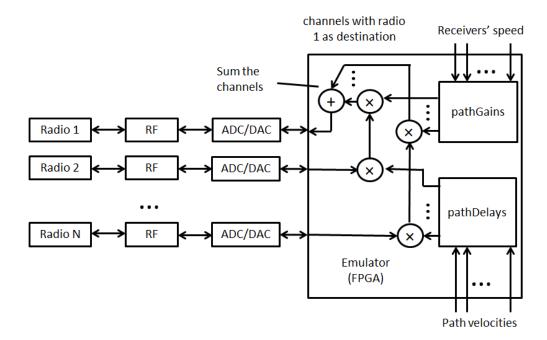

| Figure 2.2. | System overview of the wireless channel emulator                                                                                                     | 27 |

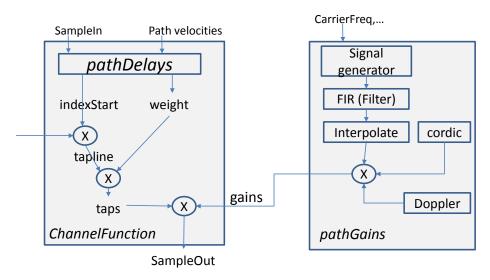

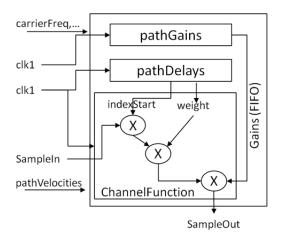

| Figure 2.3. | A block diagram of the channel emulator, which includes three main functions <i>ChannelFunction</i> , <i>PathGains</i> and <i>PathDelays</i>         | 30 |

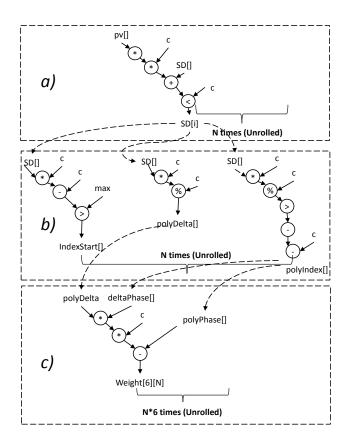

| Figure 2.4. | The final restructured <i>PathDelays</i> code. There are three blocks: (a) sample delay calculation, (b) index calculation, (c) weight calculation   | 31 |

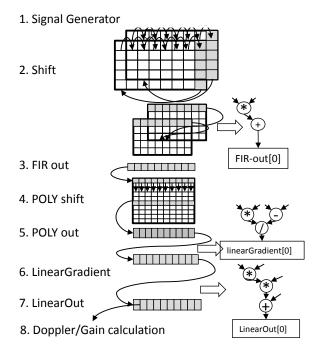

| Figure 2.5. | The computation involved in the PathGains module                                                                                                     | 32 |

| Figure 2.6. | Optimizations on the <i>PathGains</i> module including: (a) Loop merging, (b) Expression balancing, (c) Loop unrolling                               | 35 |

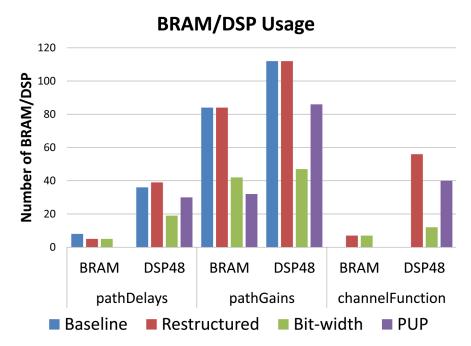

| Figure 2.7. | Number of BRAM/DSP for Baseline, Restructured, Bit-width and PUP optimizations for <i>PathDelays</i> , <i>PathGains</i> and <i>ChannelFunction</i> . | 42 |

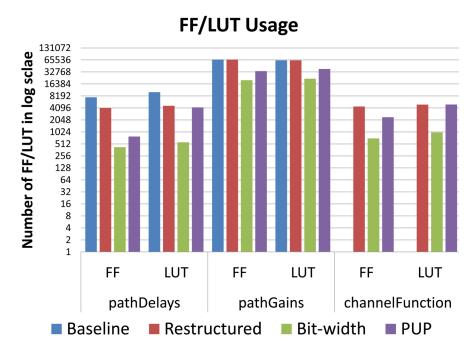

| Figure 2.8. | Number of FF/LUT for Baseline, Restructured, Bit-width and PUP optimizations of <i>PathDelays</i> , <i>PathGains</i> and <i>ChannelFunction</i>      | 43 |

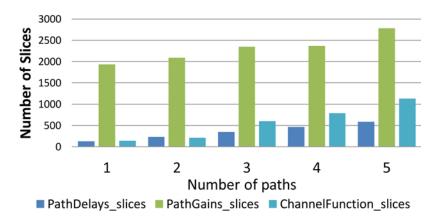

| Figure 2.9. | Slice numbers for scaling number of paths                                                                                                            | 44 |

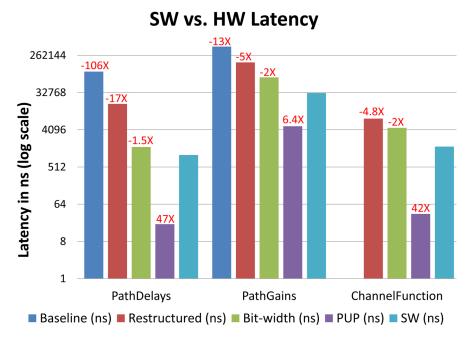

| Figure 2.10. | width and PUP optimizations of <i>PathDelays</i> , <i>PathGains</i> and <i>ChannelFunction</i> . Negative (-X) means slower by X than software(SW). Positive X means faster by X than software                             | 45 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

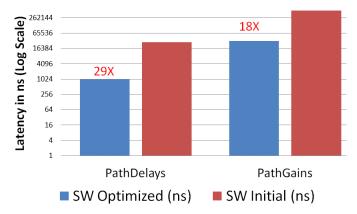

| Figure 2.11. | Performance of initial and optimized versions of software for <i>PathDelays</i> and <i>PathGains</i>                                                                                                                       | 46 |

| Figure 2.12. | Block diagram of the emulator                                                                                                                                                                                              | 46 |

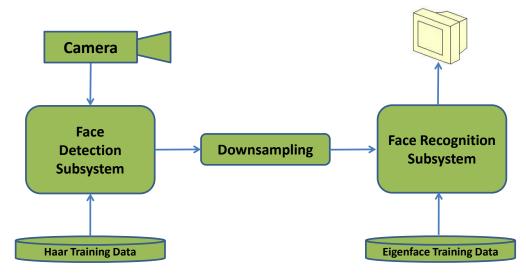

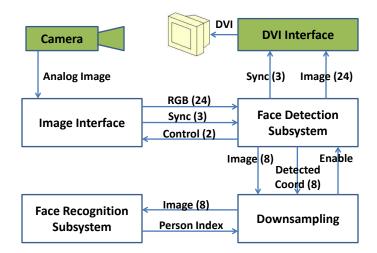

| Figure 3.1.  | Overview of our complete face recognition system on an FPGA                                                                                                                                                                | 52 |

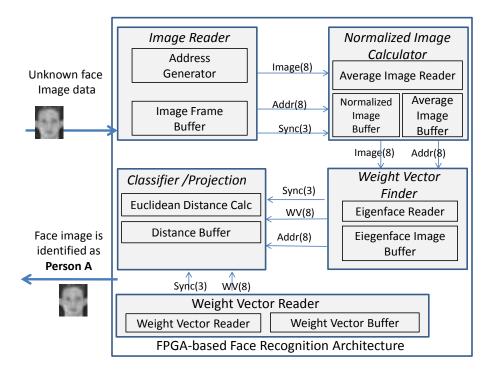

| Figure 3.2.  | The block diagram of face recognition subsystem implemented on Virtex-5 FPGA                                                                                                                                               | 53 |

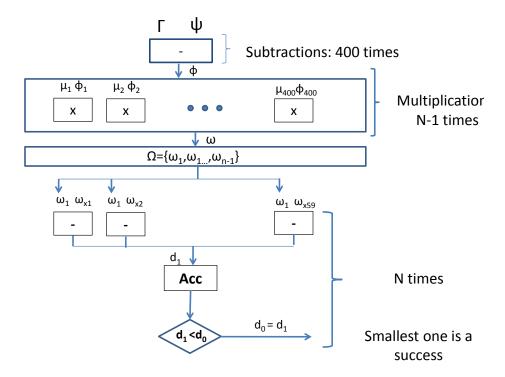

| Figure 3.3.  | The architecture of face recognition subsystem                                                                                                                                                                             | 57 |

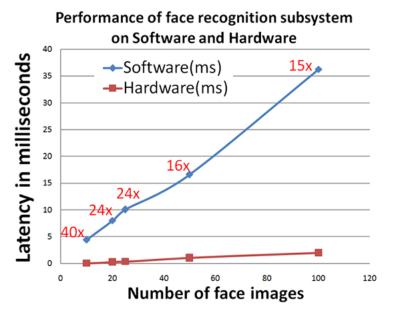

| Figure 3.4.  | The performance comparisons between software and hardware implementation of the face recognition subsystem                                                                                                                 | 59 |

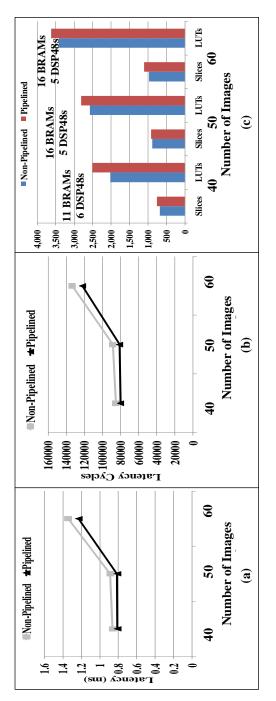

| Figure 3.5.  | Part (a) shows the latency of our face recognition subsystem implementation results on a Virtex 5 FPGA in milliseconds using 40, 50 and 60 images from <i>set2</i> using both pipelined and non-pipelined implementations. | 61 |

| Figure 3.6.  | The architecture for the complete face recognition system consisting of the face detection and face recognition subsystems                                                                                                 | 62 |

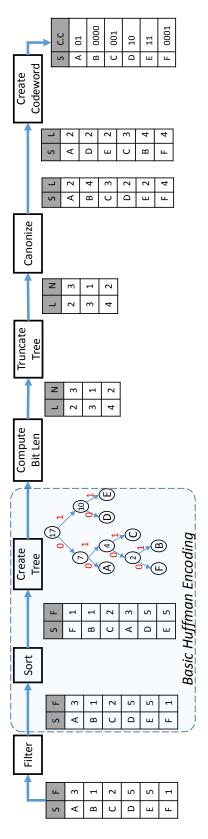

| Figure 4.1.  | The Canonical Huffman Encoding process                                                                                                                                                                                     | 67 |

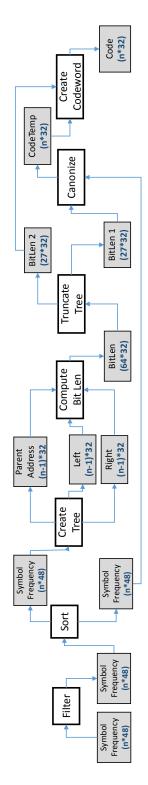

| Figure 4.2.  | The block diagram for our hardware implementation of canonical Huffman encoding. The gray blocks represent BRAMs with its size in bits. The white blocks correspond to the computational cores                             | 71 |

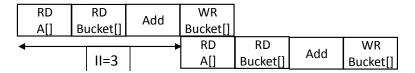

| Figure 4.3.  | A naively optimized code has RAW dependencies which requires an $II = 3$ .                                                                                                                                                 | 73 |

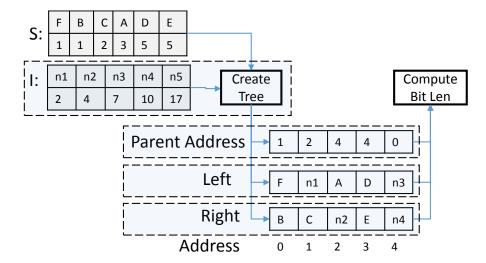

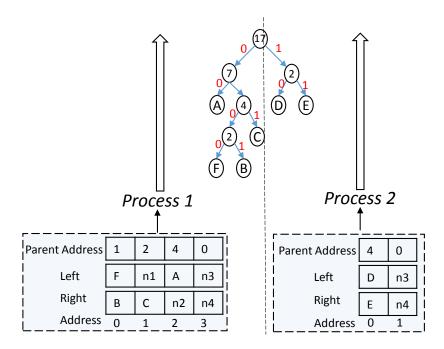

| Figure 4.4.  | The architecture for efficient Huffman tree creation. This architecture creates a Huffman tree in one pass by avoiding resorting of the elements.                                                                          | 74 |

| Figure 4.5.  | A Parallel Bit Lengths Calculation. Each process has its own set of data which allows for fully parallel bit length calculation                                                                                            | 76 |

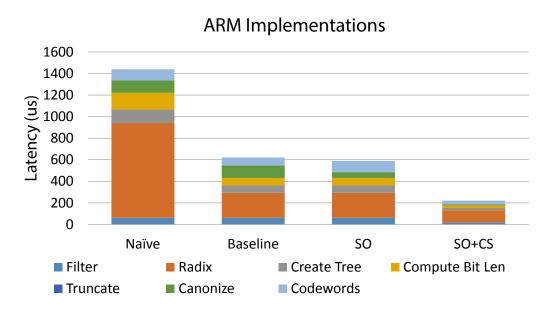

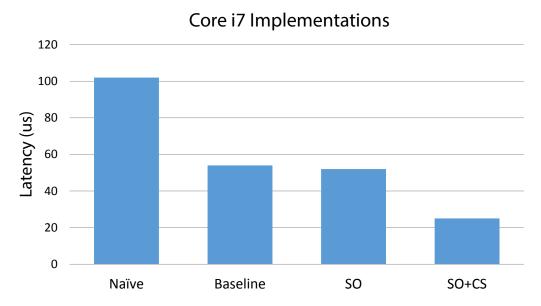

| Figure 4.6.  | The latency results of the various software implementations running on an ARM Cortex-A9 processor.                                                                                                                                                       | 81  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.7.  | The latency results of the various software implementations running on an Intel Core i7 processor                                                                                                                                                        | 82  |

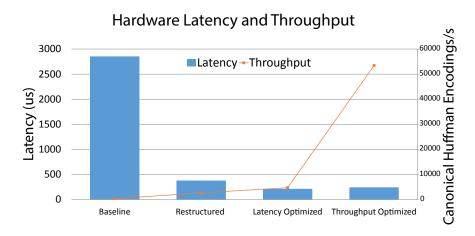

| Figure 4.8.  | The latency and throughput of hardware implementations                                                                                                                                                                                                   | 82  |

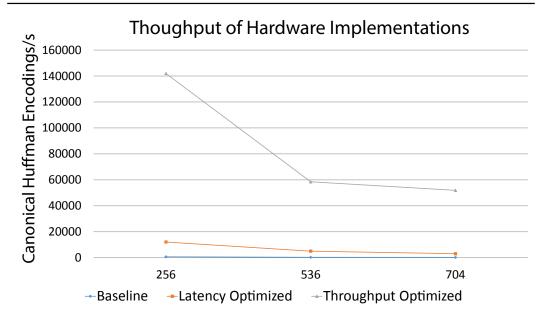

| Figure 4.9.  | The throughput of hardware implementation for different input sizes.                                                                                                                                                                                     | 83  |

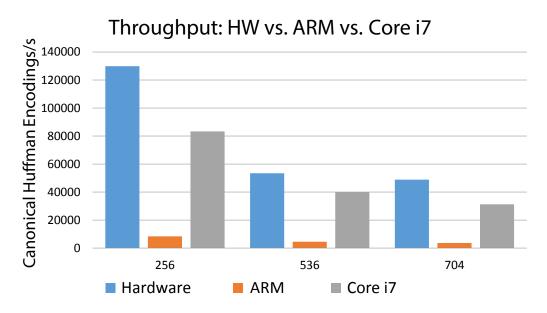

| Figure 4.10. | Throughput for different input sizes: HW vs. ARM vs. Core i7                                                                                                                                                                                             | 84  |

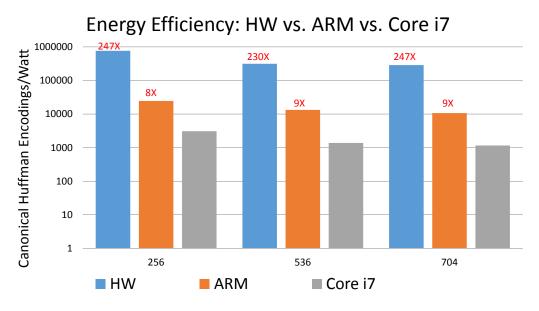

| Figure 4.11. | Power efficiency for various input sizes: HW vs. ARM vs. Core i7                                                                                                                                                                                         | 86  |

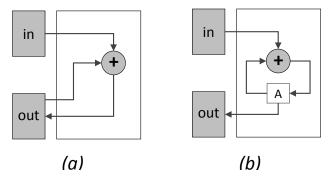

| Figure 5.1.  | Part a) is the hardware architecture created by the code in Listing 5.1. Part b) is the hardware architectures corresponding to the restructured code in Listing 5.3. Breaking the dependency between the <i>out</i> array creates a more optimal design | 96  |

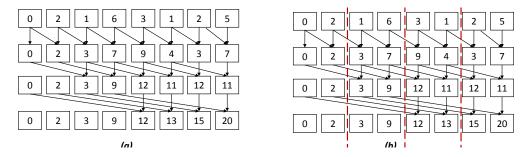

| Figure 5.2.  | a) Eight input prefix sum using reduction. b) A potential partitioning of the prefix sum.                                                                                                                                                                | 97  |

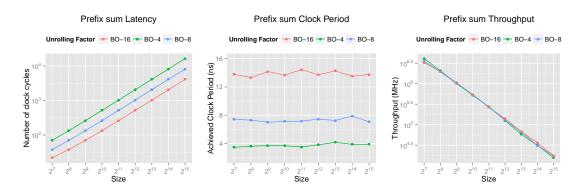

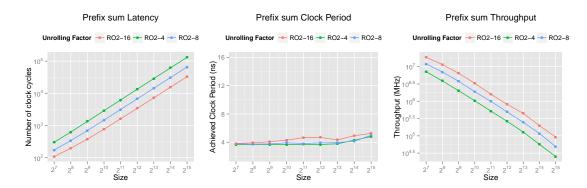

| Figure 5.3.  | Results of prefix sum for Baseline Optimized                                                                                                                                                                                                             | 97  |

| Figure 5.4.  | Results of prefix sum for Restructured Optimized 1                                                                                                                                                                                                       | 98  |

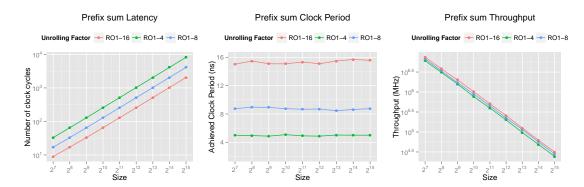

| Figure 5.5.  | Results of prefix sum for Restructured Optimized 2                                                                                                                                                                                                       | 99  |

| Figure 5.6.  | A histogram kernel counts the occurrences of the elements in a set of data.                                                                                                                                                                              | 100 |

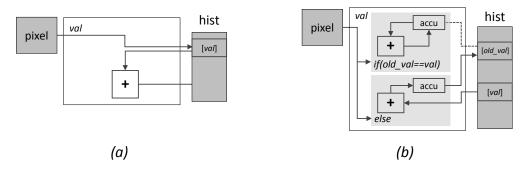

| Figure 5.7.  | Hardware architectures created by software code versus hardware architectures created by restructured code for prefix sum                                                                                                                                | 101 |

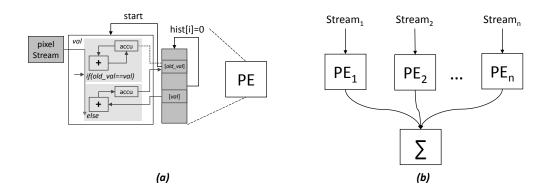

| Figure 5.8.  | Histogram: a) PE for histogram, b) Communicating PEs                                                                                                                                                                                                     | 102 |

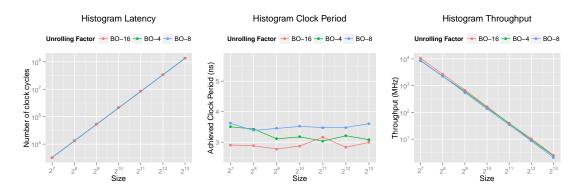

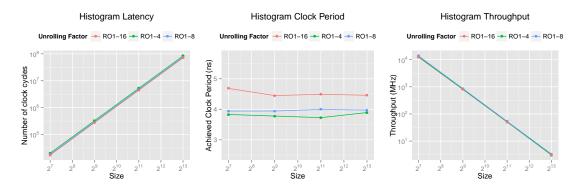

| Figure 5.9.  | Baseline Optimized (BO) implementation of the histogram kernel. The latency does not scale based on unroll factor. Clock period varies between 2.75-3.75 ns. Thus, the throughput for the different unrolled architectures are very similar.             | 104 |

| Figure 5.10. | Histogram: <i>Restructured Optimized 1</i> . Latency decreases from <i>Baseline Optimized</i> and does not scale based on unroll factor. Clock period varies between 3.75-4.75 nano seconds. Throughput increases little bit.                            | 104 |

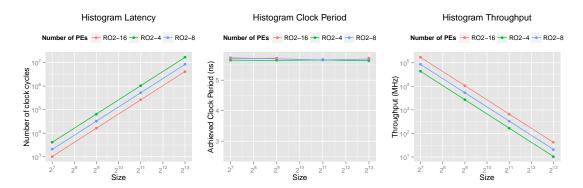

| Figure 5.11. | Histogram: <i>Restructured Optimized</i> 2. RO-4,RO-8, RO-16 are designs with different number of PEs. Latency does scale based on the number of PEs. Clock period varies between 5.54-5.75 nano seconds. Throughput scales based on the number of PEs | 105 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

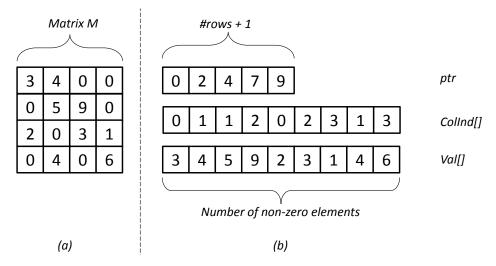

| Figure 5.12. | a) A sparse matrix (normal representation) $M$ of size $4 \times 4$ , b) Compressed Sparse Row matrix (CSR) format for $M$                                                                                                                             | 106 |

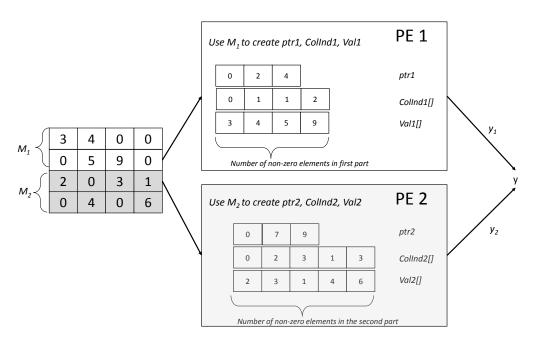

| Figure 5.13. | a) Hardware architecture of a sparse matrix vector multiplication.                                                                                                                                                                                     | 111 |

| Figure 5.14. | a) Hardware architecture of a sparse matrix vector multiplication using two PEs                                                                                                                                                                        | 111 |

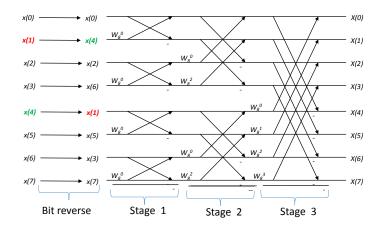

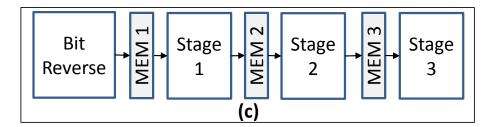

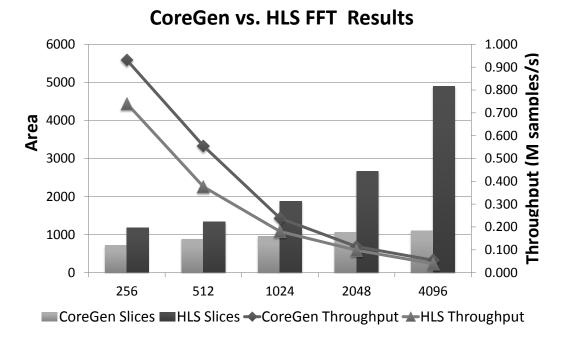

| Figure 5.15. | An 8-point FFT. The first stage swaps the data using a bit reverse algorithm. The next three stages perform butterfly operations                                                                                                                       | 113 |

| Figure 5.16. | Block diagram of FFT                                                                                                                                                                                                                                   | 116 |

| Figure 5.17. | Hardware area and throughput results of our FFT and CoreGen FFT.                                                                                                                                                                                       | 117 |

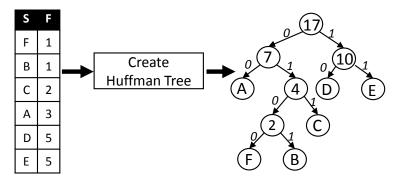

| Figure 5.18. | Huffman Tree: S=Symbol, F=Frequency                                                                                                                                                                                                                    | 118 |

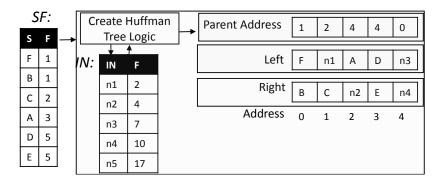

| Figure 5.19. | Hardware architecture of HuffmanCreateTree module: SF is an array storing symbol in S and frequency in F. IN is an array storing symbol in IN field and frequency in F field                                                                           | 121 |

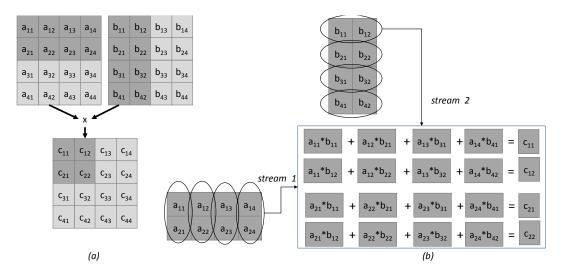

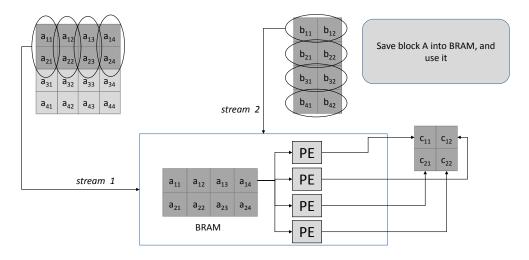

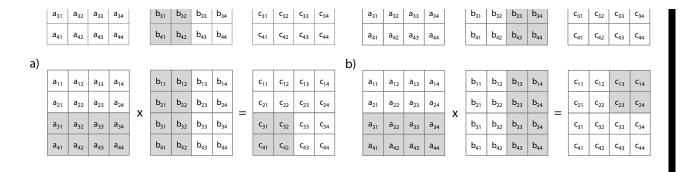

| Figure 5.20. | Hardware architecture for blocking matrix multiplication                                                                                                                                                                                               | 124 |

| Figure 5.21. | Details of hardware architecture for blocking matrix multiplication                                                                                                                                                                                    | 125 |

| Figure 5.22. | Sequences of blocks to be sent to blocking matrix multiplication .                                                                                                                                                                                     | 125 |

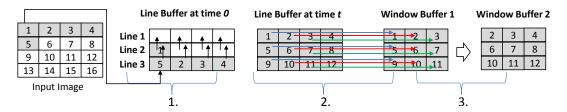

| Figure 5.23. | Line buffer and window buffer example for convolution operation.                                                                                                                                                                                       | 128 |

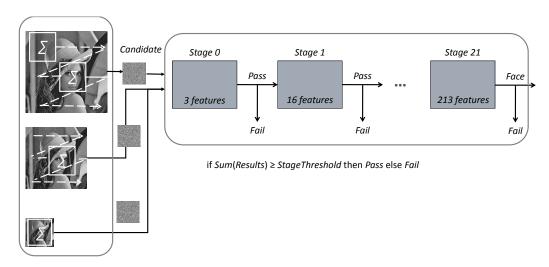

| Figure 5.24. | Hardware oriented face detection                                                                                                                                                                                                                       | 134 |

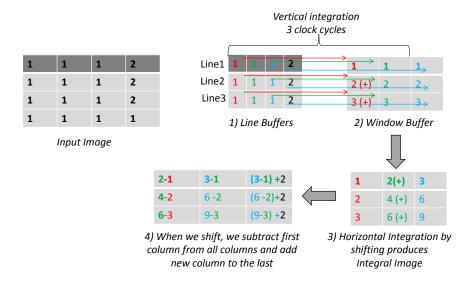

| Figure 5.25. | Integral image calculation hardware architecture for $4 \times 4$ size image.                                                                                                                                                                          | 136 |

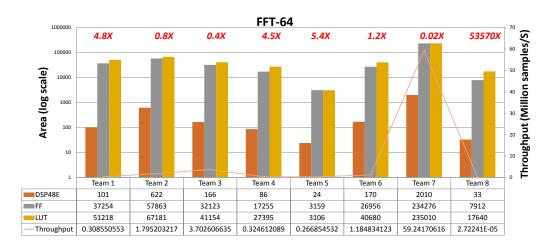

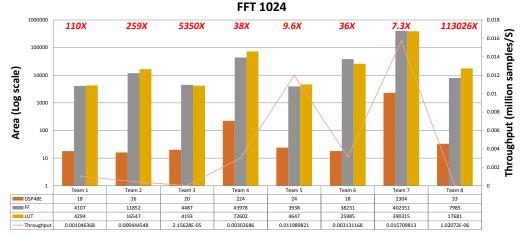

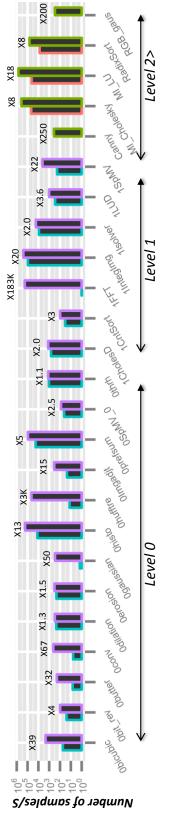

| Figure 5.26. | Hardware area and performance (throughput) results for FFT-64                                                                                                                                                                                          | 141 |

| Figure 5.27. | Hardware area and performance (throughput) results for FFT-1024.                                                                                                                                                                                       | 141 |

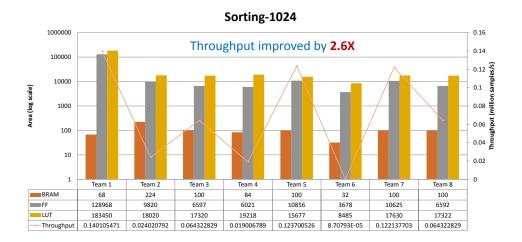

| Figure 5.28. | Hardware area and performance (throughput) results for Sorting-<br>1024.                                                                                                                                                                               | 143 |

| Figure 5.29. | Hardware area and performance (throughput) results for Sorting-<br>16384                                                                                                                   | 143 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

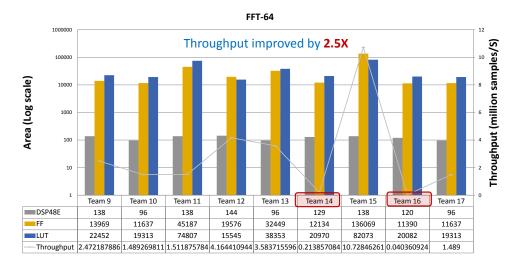

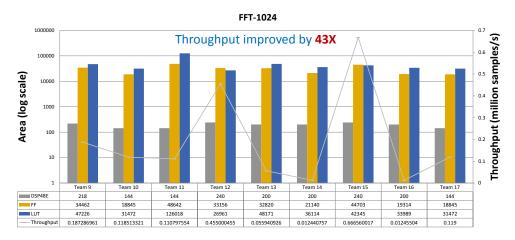

| Figure 5.30. | Hardware area and performance (throughput) results for FFT-64 after providing templates                                                                                                    | 145 |

| Figure 5.31. | Hardware area and performance (throughput) results for FFT-1024 after providing templates                                                                                                  | 145 |

| Figure 5.32. | Hardware area and performance (throughput) results for Sorting-<br>1024 after providing templates                                                                                          | 146 |

| Figure 5.33. | Hardware area and performance (throughput) results for Sorting-<br>16384 after providing templates                                                                                         | 146 |

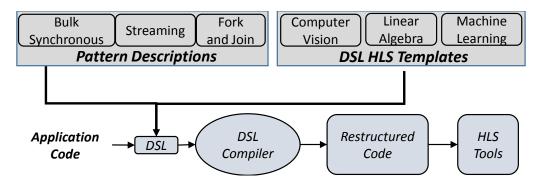

| Figure 5.34. | Design flow for software programmers using HLS templates (restructured code) and parallel programming patterns                                                                             | 149 |

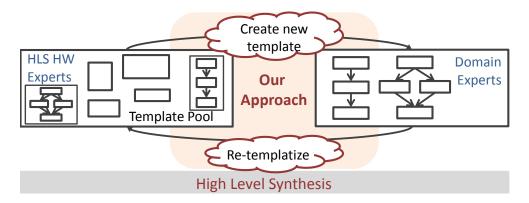

| Figure 6.1.  | An abstraction layer that separates domain knowledge from hardware skills                                                                                                                  | 153 |

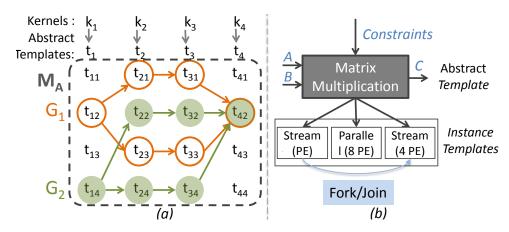

| Figure 6.2.  | Hierarchically composing templates from primitive templates                                                                                                                                | 157 |

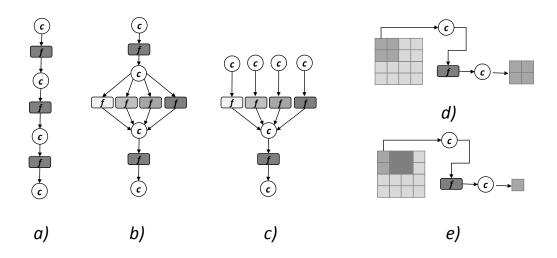

| Figure 6.3.  | Patterns. a) Bulk synchronous, b) Fork/Join, c) Merge, d) Tiled computation, e) Sliding window. Symbol $c$ refers to channel. Channel is a communication medium such as a fifo or a memory | 159 |

| Figure 6.4.  | Composition example. a) Bulk-synchronous model, b) An example relationship between abstrat and instance templates                                                                          | 164 |

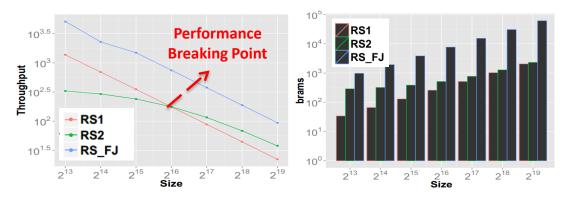

| Figure 6.5.  | The performance of OSC versus Templates                                                                                                                                                    | 167 |

| Figure 6.6.  | <ul><li>(a) Performance graph showing performance breaking point (PBP).</li><li>Templates provide a means to select right tempalte based on PBP.</li><li>(b) Area</li></ul>                | 168 |

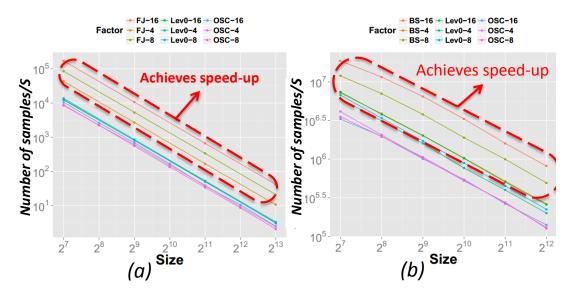

| Figure 6.7.  | Developing parameterizable templates for a) Histogram, b) Prefix-<br>sum                                                                                                                   | 170 |

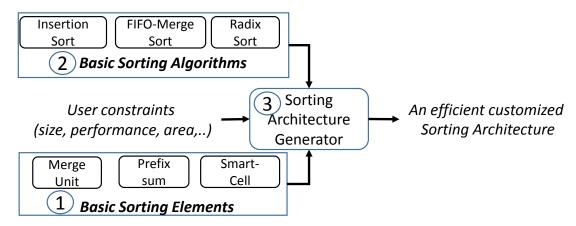

| Figure 7.1.  | The sorting framework                                                                                                                                                                      | 178 |

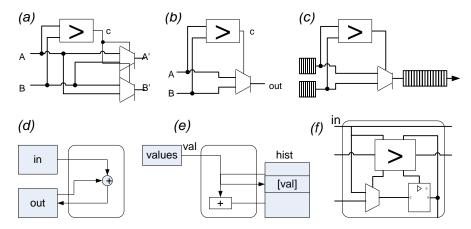

| Figure 7.2.  | Initial hardware architecture of sorting primitives generated from HLS. a) compare-swap, b) select-value element, c) merge, d) prefix-sum, e) histogram, f) insertion cell                 | 180 |

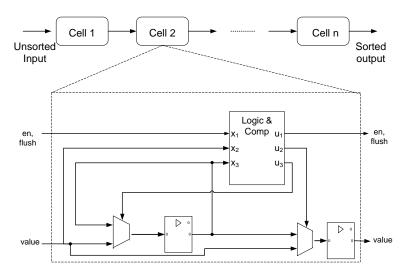

| Figure 7.3. | Hardware architecture of linear insertion sort                                                          | 184 |

|-------------|---------------------------------------------------------------------------------------------------------|-----|

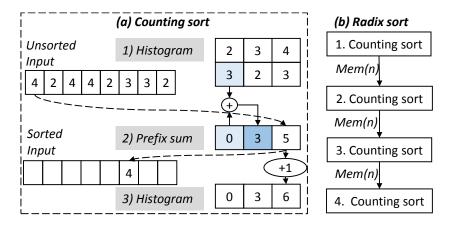

| Figure 7.4. | An example hardware architectures for counting sort and radix sort                                      | 188 |

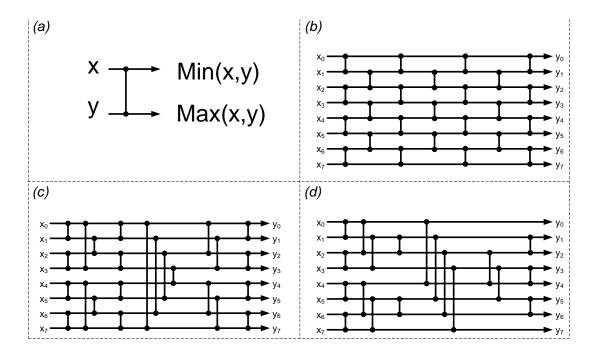

| Figure 7.5. | Sorting networks. a) Odd-even trans sort (Bubble sort), b) Bitonic sort, b) Odd-even transposition sort | 189 |

| Figure 7.6. | Grammar of domain-specific language                                                                     | 190 |

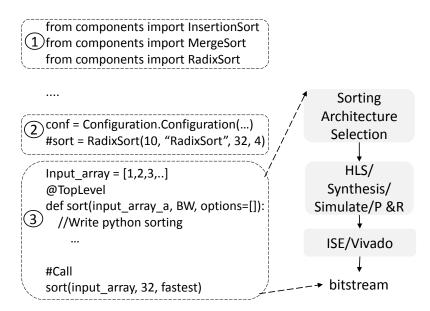

| Figure 7.7. | Sorting architecture generation                                                                         | 191 |

## LIST OF TABLES

| Table 1.1. | Vivado HLS directives to optimize throughput and latency                                                 | 16  |

|------------|----------------------------------------------------------------------------------------------------------|-----|

| Table 1.2. | Vivado HLS directives to optimize area                                                                   | 17  |

| Table 2.1. | Device utilization characteristics for PathDelays, PathGains and ChannelFunction for five paths.         | 41  |

| Table 2.2. | Clock cycles, clock period and latency of each sub module                                                | 41  |

| Table 2.3. | Device utilization characteristics of complete emulator for emulators integrated by AutoESL and Manually | 41  |

| Table 3.1. | Device Utilization Table for the Complete Face Recognition System                                        | 62  |

| Table 4.1. | Hardware area and performance results                                                                    | 83  |

| Table 5.1. | Optimizations on a sparse matrix-vector multiplication                                                   | 109 |

| Table 5.2. | Huffman Tree Creation                                                                                    | 122 |

| Table 5.3. | Convolution.                                                                                             | 131 |

| Table 5.4. | Integral Image Creation.                                                                                 | 138 |

| Table 5.5. | User Study-1.                                                                                            | 140 |

| Table 5.6. | User Study-2                                                                                             | 144 |

| Table 6.1. | Hardware area and performance results                                                                    | 175 |

| Table 7.1. | Sorting Algorithms evaluations when implementing them using HLS.                                         | 179 |

| Table 7.3. | Area and performance of End-to-End demo                                                                  | 196 |

| Table 7.4. | Streaming insertion sort generated in this paper vs. Interleaved linear insertion sorter [104]           | 196 |

### **ACKNOWLEDGEMENTS**

First and foremost I wish to thank my advisor Professor Ryan Kastner. This thesis would not have been possible without his support over these years. I am grateful for the friendly research environment provided by him, and for encouraging me to do research during the initial years of my PhD studies. I am also grateful to Ryan for providing me with the opportunity to get involved in the curriculum development process for the MAS WES program at UCSD where I learned many technical and life lessons.

I would like to thank Dr. Ali Irturk for his assistance during the initial stages of my PhD. His comments have greatly improved the quality of my research. I also would like to thank Dr. Juanjo Noguera and Dr. Stephen Neuendorffer at Xilinx Research Labs for providing an amazing internship experience during the summer of 2011. I owe special thanks to Dr. Stephen Neuendorffer at Xilinx for answering many of my technical questions even after my internship. I also like to thank Dr. Joo-Young Kim for the amazing intern experience at MSR and providing the chance to participate in the cutting-edge research project.

I also would like to thank my committee members. I thank them for allocating their valuable time for my thesis proposal and final defense from their busy schedule.

I am indebted to many of my colleagues for fun and positive environment. I am especially thankful for Jason Oberg, Dustin Richmond, Alric Althoff and Perry Naughton for their assistance during these years for helping me to polish my paper writing process.

This journey would not have been possible without the support of all my family members located half way around the world. I thank my parents and parents-in-law for their love. I am always thankful to my brothers and sisters for supporting me during these years even they were so far away. Last but not least, I am grateful to my wife for tolerating my ignorance and my daughters for being nice kids during these years when "Daddy" was a student.

Chapter 2 contains materials as they appear in International Conference on Field-Programmable Technology (FPT), 2012. Matai, Janarbek; Meng, Pingfan; Wu, Lingjuan; Weals, Brad; Kastner, Ryan. The chapter also contains additional materials (mainly larger figures) that were cut from the publication due to space constraints. The dissertation author is the primary investigator and author of this work.

Chapter 3 contains materials from a work that was published in International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2011. Matai, Janarbek; Irturk, Ali; Kastner, Ryan. The chapter also contains additional materials that were omitted from the publication due to space constraints. The dissertation author is the primary investigator and author of this work.

Chapter 4 contains contains material as it appears in the 25th IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), 2014. Matai, Janarbek; Kim, Joo-Young; Kastner, Ryan. The dissertation author is the primary investigator and author of this work.

Chapter 5 contains materials printed in First International Workshop on FPGAs for Software Programmers (FSP 2014). Matai, Janarbek; Richmond, Dustin; Lee, Dajung; Kastner, Ryan. This chapter also contains significant amount of new materials not included in the publication. The dissertation author is the primary investigator and author of this work.

Chapter 6 contains materials from our current work. This work is to be submitted to relevant conference in March, 2015. Matai, Janarbek; Lee, Dajung; Alric Althoff; Kastner, Ryan. The dissertation author is the primary investigator and author of this work.

Chapter 7 contains materials currently in progress. Matai, Janarbek; Richmond, Dustin; Lee, Dajung; Zac Blair; Kastner, Ryan. The dissertation author is the primary investigator and author of this work.

#### **VITA**

| 2004 | Bachelor of Science, Mongolian University of Science and Technology                       |

|------|-------------------------------------------------------------------------------------------|

| 2007 | Master of Science, Korea Advanced Institute of Science and Technology (former ICU Campus) |

| 2009 | Electronics and Telecommunications Research Institute                                     |

| 2015 | Doctor of Philosophy, University of California, San Diego                                 |

### **PUBLICATIONS**

Janarbek Matai, Dustin Richmond, Dajung Lee, Zac Blair, and Ryan Kastner. "Resolve: Computer Generation of High-Performance Sorting Architectures from High-Level Synthesis." to be submitted within 2015

Janarbek Matai, Dajung Lee, Alric Althoff, and Ryan Kastner. "Composable, Parameterizable Templates for High Level Synthesis." to be submitted.

Quentin Gautier, Alexandria Shearer, Janarbek Matai, Dustin Richmond, Pingfan Meng, and Ryan Kastner. "Real-time 3D Reconstruction for FPGAs: A Case Study for Evaluating the Performance, Area, and Programmability Trade-offs of the Altera OpenCL SDK." In International Conference on Field-Programmable Technology (FPT), 2014.

Janarbek Matai, Dustin Richmond, Dajung Lee, and Ryan Kastner. "Enabling FPGAs for the Masses." In Proceedings of the First International Workshop on FPGAs for Software Programmers (FSP), 2014

Dajung Lee, Janarbek Matai, Brad Weals, and Ryan Kastner. "High throughput channel tracking for jtrs wireless channel emulation." In Proceedings of the 24th International Conference on Field Programmable Logic and Applications (FPL), 2014

Janarbek Matai, Joo-Young Kim, and Ryan Kastner. "Energy Efficient Canonical Huffman Encoding." In Proceedings of the The 25th IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), 2014

Motoki Kimura, Janarbek Matai, Matthew Jacobsen, and Ryan Kastner. "A low-power Adaboost-based object detection processor using Haar-like features." In Proceedings of the Third International Conference on Consumer Electronics Berlin (ICCE-Berlin), 2013.

Janarbek Matai, Pingfan Meng, Lingjuan Wu, Brad T. Weals, and Ryan Kastner. "Designing a hardware in the loop wireless digital channel emulator for software defined radio." In Proceedings of the International Conference on Field-Programmable Technology, 2012.

Janarbek Matai, Jason Oberg, Ali Irturk, Taemin Kim, and Ryan Kastner. "Trimmed VLIW: Moving application specific processors towards high level synthesis." In Proceedings of the Electronic System Level Synthesis Conference (ESLsyn), 2012.

Janarbek Matai, Ali Irturk, and Ryan Kastner. "Design and implementation of an FPGA-based real-time face recognition system." In Proceedings of the 19th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2011.

### ABSTRACT OF THE DISSERTATION

Templates and Patterns: Augmenting High-Level Synthesis for Domain-Specific Computing

by

Janarbek Matai

Doctor of Philosophy in Computer Science

University of California, San Diego, 2015

Professor Ryan Kastner, Chair

Implementing an application on a FPGA remains a difficult, non-intuitive task that often requires hardware design expertise in a hardware description language (HDL). High-level synthesis (HLS) raises the design abstraction from HDL to languages such as C/C++/Scala/Java. Despite this, in order to get a good quality of result (QoR), a designer must carefully craft the HLS code. In other words, HLS designers must implement the application using an abstract language in a manner that generates an efficient microarchitecture; we call this process writing restructured code. This reduces the benefits of implementing the application at a higher level of abstraction and limits the impact of HLS

by requiring explicit knowledge of the underlying hardware architecture. Developers must know how to write code that reflects low level implementation details of the application at hand as it is interpreted by HLS tools. As a result, FPGA design still largely remains job of either hardware engineers or expert HLS designers. In this work, we aim to take a step towards making HLS tools useful for a broader set of programmers. To do this, we made following contributions: 1) we study methodologies of restructuring software code for HLS tools; 2) we provide examples of designing different kernels in state-of-the art HLS tools; 3) we described a theoretical framework for parameterizable HLS templates for composing restructured HLS code based on design patterns, 4) we present a domain-specific framework that generates efficient FPGA designs using pre-optimized HLS templates and design patterns.

## Introduction

Two clear trends have emerged in computing in the past 5-10 years: power consumption and processing massive amounts of data. Power consumption become a major metric in all areas of computing platforms from mobile devices to datacenters. We want our smart phones to last longer and datacenters to consume less power while still achieving massive computation.

Big data has reached into almost all industries to improve the quality of service. Machine learning algorithms process thousands of images to create classifiers, search engines analyse billions of search queries to find relevant data, and weather forecast systems analyse massive amounts of historical data to make better predictions. Massive data processing comes at a price. It requires huge computational power or high-performance computers. Thus, we need high-performance computers with efficient power consumption to run computationally demanding applications. The state of the art high-performance platforms (built using CPUs or GPUs) for computational expensive applications are not energy efficient.

Recently researchers have suggested using specialized hardware accelerators as one of the solutions to the worsening power consumption of computational platforms [127, 40, 111], among others. Specialized hardware is developed on different platforms such as FPGA (Field-Programmable Gate Array) or ASIC (Application-Specific Integrated Circuit). Designing an ASIC is expensive and have low time-to-market. Flexibility and programmability of FPGA makes it a primary platform to develop specialized

hardware. FPGAs are seeing widespread adoption in applications, including wireless communication, image processing, and datacenter (e.g., [111]). Despite the increasing use in these application domains, programming an FPGA largely requires an expert hardware designer. This severely inhibits the widespread use of these devices.

We aim to raise the level of programming abstraction to allow designers that have limited or ideally no understanding of the underlying hardware architecture to implement their application of choice on an FPGA. This has been the goal of numerous academic and industrial projects, many of which fall into the domain of high-level synthesis (HLS). There has been tremendous progress in the development of HLS tools since its introduction over three decades ago; however, there are several existing challenges that still hinder the ability for any designer to program an FPGA using HLS.

First and foremost, designers cannot effectively use existing HLS tools unless they have intimate knowledge of micro-architectural trade-offs. Even the best HLS tools require at least a two stage code transformation to generate efficient hardware. The initial design process converts a "normal" C application description to code that is synthesizable by the HLS tools. This is done by removing unsupported programming constructs, e.g., dynamic memory allocation [137, 57]. Then this synthesizable C code undergoes an additional conversion where it is rewritten to take advantage of specific micro-architectural features; we call this process developing "restructured" code. This must adhere to strict coding styles that are dictated by the HLS tool and the target device [13, 113]. This two stage code transformation process presents several challenges. It requires that the designer understand how to develop code that exploits low-level micro-architectural features using an abstract language. These are often not easily specified using that language, and typically require intimate knowledge of the HLS tool as well as significant hardware design expertise.

In summary, while HLS tools are meant to be used by a larger number of designers

and increase productivity, creating an optimized implementation requires substantial hardware design skills. Thus in order to successfully use today's HLS tools one needs to have: 1) domain knowledge about the application, 2) hardware design expertise, and 3) the ability to translate the domain knowledge into an efficient hardware design.

The goal of this dissertation is to make specialized hardware design process (built on FPGAs) easier so that wide variety of people (scientists and software programmers) can benefit from FPGA's high-performance and low power. Our approach is based on the observation that certain application domains have a number of basic kernels that share similar computational primitives. This indicates that these kernels can and should be generated from highly optimized templatized architectures. Based on this observation, we develop an approach based upon parameterizable templates that can be composed using common design (computational and structural) patterns. These templates describe an efficient hardware architecture for a wide variety of commonly occurring kernels for certain application domains. Common design patterns orchestrate these templates in different ways to build large complex applications.

Patterns take advantage of the fact that the task-level parallelism in many applications is organized in a structured manner. Different kernels of applications designed with templates communicate in a certain pattern. Examples of patterns are functional pipelining (bulk synchronous), Fork/Join, Merge, sliding window, and tiled computations (e.g., tiled matrix multiplication). By using these patterns and templates, we can form new templates (by composing) which can be added to the existing template pool.

In this dissertation, we present a set of reusable and optimized templates for HLS that forms a new template based on specific design (computational and structural) patterns. We propose a domain-specific framework that generates optimized HLS code without requiring any low level hardware details using reusable templates and patterns. Next, we list the main contributions of this research in the order they appear in this

### dissertation:

- Study of several application designs using high-level synthesis. These application

designs provided initial guiding principles for efficient FPGA design using HLS.

Some of these applications are: High Throughput Wireless Channel Emulator, Face

Recognition, and Canonical Huffman Encoding.

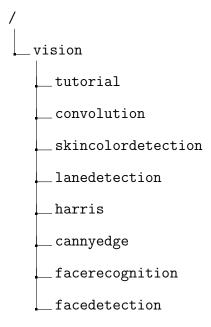

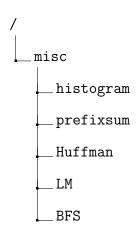

- 2. Building restructured code and coding techniques for a number of application kernels for different application domains; computer vision, linear algebra and data processing (sorting).

- 3. An experimental study about evaluating usage of pre designed templates to design FPGA hardware.

- 4. A theoretical treatment of the composibility and parameterization of templates (based on patterns) in order to combine basic templates into more complex ones that can be used to build complex applications based on specific computational patterns.

- 5. A case study of generating optimized FPGA designs from templates based on a domain-specific framework. Specifically, we presented a framework, Resolve, which generates optimized HLS code from a simple domain-specific language written in python using templates.

- 6. The development of basic templates across application domains and their open source implementations.

To assist the reader of this thesis, we now give a brief overview of each chapter. Chapter 1 presents a brief overview of high-level synthesis. We first discuss the force-directed scheduling algorithm, then we introduce Vivado HLS, a high-level synthesis

tool used in this dissertation. Finally, we will present a simple "'Hello World" in Vivado HLS and give an overview of some of the issues in current HLS tools.

Chapter 2, Chapter 3 and Chapter 4 present three application case studies using high-level synthesis to design FPGA hardware. These applications demonstrate issues and promises of the current high-level synthesis design approach. In Chapter 2, we present a design flow of using high-level synthesis for a wireless channel emulator. The goal of this chapter is to introduce the design flow of high-level synthesis for real world application and to demonstrate a variety of results obtained by HLS optimization. Chapter 3 demonstrates design and implementation of face recognition on an FPGA. The goal of this chapter is to introduce designing regular applications with HLS. Chapter 4 presents design and implementation of Canonical Huffman encoding used for datacenter applications. The goal of this chapter is to demonstrate design and implementation of irregular applications using high-level synthesis. Based on experiences gained designing these applications, we present restructured code in following chapter.

In chapter Chapter 5, we formally define restructured code and present examples of restructured code. First, we present a study on the importance of restructuring code to obtain an efficient FPGA designs with good QoR (Quality of Result). We present several case studies of code restructuring in different levels (instruction and task level) for different kernels. We also present a small survey about using HLS to design applications on an FPGA.

Chapter 6 presents a composable template based on the restructured code presented in chapter Chapter 5. The main contribution of this chapter is providing a theoretical framework for the treatment of the composibility and parameterization of templates in order to combine basic templates into more complex ones based on patterns.

Chapter 7 presents a framework that generates sorting architectures automatically by composing existing templates. In this chapter, we cover design and implementation of sorting architectures. Then we present a domain-specific framework that generates sorting architectures automatically based on sorting templates and patterns.

Chapter 8 presents conclusion and future research directions of this thesis.

# **Chapter 1**

# **Background**

## 1.1 Introduction

There are many embedded applications such as computer vision/graphics, digital signal processing, wireless communications which benefit from field-programmable gate arrays (FPGAs). An FPGA is a reconfigurable hardware platform which can be configured after manufacturing. Due to their reconfigurable nature, FPGAs are good platform for many of these applications because they provide a good trade-off between performance and power consumption. Traditionally, FPGA systems are programmed using low level Hardware Description Languages (HDL) such as Verilog/VHDL. While programming an FPGA with HDL gives a designer finer granularity control, it has drawbacks such as it requires expertise, it is expensive, and it has long time-to-market. An alternative way of designing an FPGA system is using High-Level Synthesis (HLS) tools. HLS tools allow designers to use high level languages such as C/C++ to design FPGA systems. HLS tools promise to increase productivity (decrease design time) of FPGA design, increase portability/flexibility of design, and to allow more design space exploration.

Due to its promising features, HLS has attracted the interest of both industry and academia. The first HLS tools emerged in the 1970's and targeted application-

specific integrated circuits (ASICs), before FPGA chips were introduced in 1985 [134]. Early works include HLS tools from academia such as HAL [108], Olympus\Herculeus [44, 45, 78] and HLS tools from industry such as Cathedral 2/3 [58], Yorktown Silicon Compiler [29], and Amical [73]. These works contributed largely on basic HLS research and influenced development of other tools. For example, one of the best known HLS scheduling algorithms, Force-Directed Scheduling, was first developed for the HAL system and is still used in several academic and industrial HLS works.

Since FPGA arrived on the market, many HLS tools targeting FPGA have emerged both from academia and industry. Academic efforts include SPARK [63], LegUP [30], ROCCC [129], SA-C [65], Chisel [18], NAPA-C [60], Stream-C [59], Trident [124]. Industry efforts include Vivado HLS [41] (formerly known as AutoESL), Synopsys Synphony C Compiler [9] (former name PICO), Catapult-C (Calypto) [22], Cynthesizer [92], CyberWorkBench [133], C-to-Silicon [19] DIME-C [49], Impulse-C [3], Mitron-C [6], Bluespec System Verilog [102], Synplify DSP [120], Simulink HDL Coder [118], and AccelDSP [68].

Many of these tools are based on C-like language while others are based on MATLAB, Haskell and Scala. The MATLAB based tools include Synplify DSP [120], Simulink HDL Coder [118], and AccelDSP [68]. Bluespec System Verilog [102] and Chisel [18] are based on functional programming languages such as Haskell and Scala.

Most HLS tools accept source code and optimization directives as inputs. Initial input code is usually first modified to target strict HLS requirements. This is because some constructors in the language are not supported by HLS tools such as dynamic memory allocation. This is done by replacing an unsupported part of code with equivalent code that is synthesizable. (e.g., a double pointers in C is translated into a two dimensional arrays.)

Optimization directives tell the HLS tool which part of code to optimize. In

general, most HLS tools have similar optimization directives with slightly different names. One common optimization directive is *pipeline*. This directive is given as a *pragma* in C code and pipelines loops or functions. Next, we start an introduction of basic HLS concepts followed by introduction of the Force-Directed Scheduling algorithm.

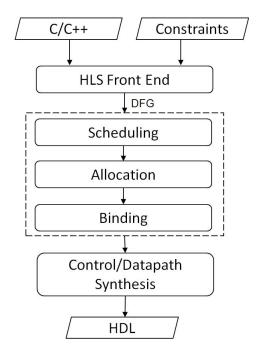

## 1.2 High-Level Synthesis

HLS tools create an architecture through several steps such as scheduling, allocation and binding process that generate different components to create a datapath [?], and each of these steps are deeply covered in [93, 54]. The general flow of high-level synthesis is shown in Figure 1.1. Initially, the HLS compiler front-end takes C/C++/Java code and transforms it to a data flow graph (DFG). The DFG is fed into high-level synthesis tool chain that does scheduling, resource allocation and binding. Scheduling is the assignment of each operation to a time slot (identifying start and end time). Resource Allocation is the process of identifying types of hardware components and the number for each type to be included in the final implementation. Binding is the process that allocates hardware components to specific operations. The final step of HLS tools is to generate HDL (Hardware Description Language) in the form of VHDL/Verilog.

In the HLS design process, designers are required to give hints and constraints in order to optimize performance. This is typically done through pragmas or other language features. Essentially, constrains are hints to a scheduler to identify the part of algorithm to optimize. Once it has its inputs (DFG, Constraints), it is the scheduler's job to define the final hardware.

In general, scheduling is most important part of any HLS tool. In next the sections, we cover one of the important HLS scheduling algorithms known as Force-Directed Scheduling.

Figure 1.1. High-Level Synthesis tool flow.

## 1.2.1 Scheduling

Scheduling is an essential component of high-level synthesis. It determines the start and end time of each operation for a given data flow graph [93, 54]. By determining start and end times of individual operations in a given data flow graph, it extracts concurrency of the resulting implementation which affects the performance and area of the final hardware.

One of the most used scheduling algorithms for high-level synthesis is the force-directed scheduling (FDS) by Paulin and Knight. [107]. The FDS algorithm employs a heuristic approach which can be applied to resource constrained scheduling as well as time constrained scheduling. The FDS algorithm is based on a concept called "force" where operations with least force are scheduled. The FDS algorithm works by first identifying time frame of an operation. The time frame is the time interval where the operation can be scheduled. In FDS, the time frame of operation is determined by ASAP

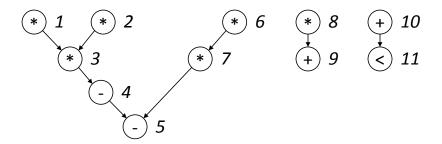

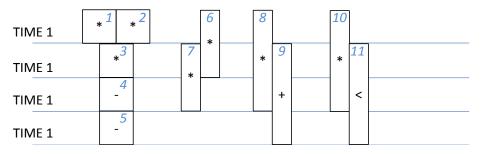

**Figure 1.2.** An example data flow graph.

(As soon as possible) and ALAP (As late as possible) scheduling algorithms. We show how ASAP and ALAP schedules are used to determine the time frame of a data flow graph in Figure 1.2. In the following, we give examples that will explain ASAP, ALAP and FDS scheduling based on [107, 93]. Figure 1.2, Figure 1.3, Figure 1.4, Figure 1.5, Figure 1.6 are also based on the same example given in [107, 93] for ASAP, ALAP and FDS scheduling.

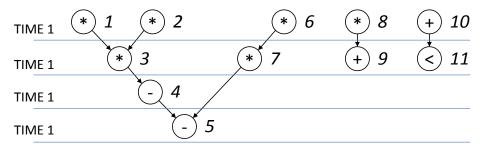

The ASAP Scheduling Algorithm: The ASAP schedule works by topologically sorting operations in a given data flow graph [93]. Topologically sorted operations are scheduled as soon as all of their dependencies (predecessors) are scheduled. The goal of this scheduling algorithm is to minimize latency (number of clock cycles) under unconstrained resources. (This does not take into account area constraints.) To illustrate, how ASAP scheduling works we use an example data flow graph in Figure 1.2 from [107]. The ASAP schedule of the data flow graph given in Figure 1.2 is show in Figure 1.3. The detailed algorithm is given in Algorithm 1.

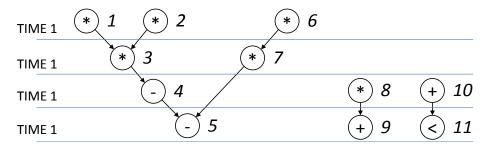

The ALAP Scheduling Algorithm: The ALAP scheduling algorithm is a latency constrained scheduling algorithm. This means, the ALAP schedule gets an upper bound  $\lambda$  on the latency input with data flow graph  $G_s$ . The ALAP algorithm is given in Algorithm 2. The ALAP schedule of the data flow graph given in Figure 1.2 is shown in Figure 1.4.

### **Algorithm 1:** ASAP Scheduling

```

1 Procedure ASAP()

Data: G_S(V,E)

/* V: Vertices, E: Edges

*/

Result: t

Schedule v_0 by setting t_0 = 1

2

repeat

3

Select a v_i whose predecessors are all scheduled;

4

Schedule v_i by setting t_i = max(t_i) + d_i

5

where j:(v_j,v_i)\in E

6

until v_n is scheduled;

```

Figure 1.3. ASAP Schedule.

**Algorithm 2:** ALAP Scheduling

**until**  $v_0$  is scheduled;

```

1 Procedure ALAP()

Data: G_S(V, E)

/* V: Vertices, E: Edges

*/

Result: t

2 Schedule v_n by setting t_n = \lambda + 1

3 repeat

4 Select a v_i successors are all scheduled;

5 Schedule v_i by setting t_i = min(t_j) - d_i

where j: (v_i, v_j) \in E

```

Figure 1.4. ALAP Schedule

Using the ASAP and ALAP scheduling results, time frames of each operation are determined as in Figure 1.5. The next step in FDS algorithm is to calculate the *operation probability* and the *type distributions* for each resource type.

Operation probability is a function that is equal to zero outside of the time frame of an operation and equal to inverse of the time frame within it (inside the time frame). We use  $p_i(l)$  to denote the operation probability of an operation i at time l. For example, for operation 6,  $p_6(1) = 0.5$ ,  $p_6(2) = 0.5$ ,  $p_6(3) = 0$  and  $p_6(1) = 0$ . (Operation 6 can only be scheduled in time slot 1 or time slot 2.) Similarly, we can determine  $p_1(1) = 1$ ,  $p_1(2) = p_1(3) = p_1(4) = 0$  and  $p_2(1) = 1$ ,  $p_2(2) = p_2(3) = p_2(4) = 0$ .

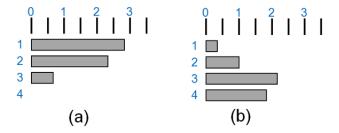

The *type distribution* is the sum of probabilities of an operation that can be executed with a specific hardware resource at time l. We use  $q_k(l)$  to denote type distribution of resource k at time l. For example, in time step 1 operations 1,3,6 and 8 can be executed with a multiplier. Thus the type distribution of the multiplier at time step 1 is equal to  $q_1(1) = p_1 1 + p_2(1) + p_6(1) + p_8(1) = 1 + 1 + 0.5 + 0.3 = 2.8$  (k=1 indicates a multiplier). Distribution graph (DG) is constructed by using type distributions from all time steps for a specific resource. The Figure 1.6 shows a DG of a multiplier and adder calculated using Equation 1.1.

There will be no horizontal bar graph(type distribution) if no operation can be schedule at a specific time. For example, no horizontal bar graph (type distribution) is shown in Figure 1.6 for a multiplier since no multiplier can not be scheduled at time step

Figure 1.5. Time frames for operations

Figure 1.6. Distribution graphs for a multiplier and adder

4.

$$DG(l) = \sum P_i(l) \tag{1.1}$$

The selection of an operation to a specific time step is governed by a concept called "force". Each operation of a data flow graph has a "force" associated with each time step. The algorithm works by a force calculation for each operation in a specific time step. The operation with the least force is then scheduled.

The force is analogous to Hooke's law F = Kx, where K is constant of a *spring*, x is the displacement and F is the force needed. In FDS algorithm, the value of distribution graph is acts like the spring constant K and the operation probability is like spring displacement. In FDS, two kinds of force are calculated for each operation: self-force and successor/predecessor force. The self-force is associated with assigning operations to specific time step and the successor/predecessor force is associated with the change

of operation dependencies. For example, scheduling the operation 6 into time step 1 changes  $p_6(1)$  from 0.5 to 0.5 (1-0.5) and  $p_6(2)$  from 0.5 to -0.5 (0-0.5). Assuming we schedule operation 6 to time step 1, we calculate self-force as 2.8\*(1-0.5)+2.3\*(0-0.5)=0.25. Similarly, when operation 6 is scheduled at time step 2, its self-force is 2.8\*(0-0.5)+2.3\*(1-0.5)=-0.25.

Assigning operation 6 to time step 2 indirectly implies that operation 7 will be assigned to step 3. In this case, we calculate successor/predecessor force of time step 7. This is added to the self-force of 6. The detailed FDS algorithm is given in Algorithm 3.

| Algorithm 3: Force Directed Scheduling           |                                         |    |

|--------------------------------------------------|-----------------------------------------|----|

| <pre>1 Procedure ForceDirectedScheduling()</pre> |                                         |    |

|                                                  | <b>Data</b> : $G_S(V,E)$                |    |

|                                                  | /* V: Vertices, E: Edges                | */ |

|                                                  | Result: t                               |    |

| 2                                                | repeat                                  |    |

| 3                                                | Compute time frames                     |    |

| 4                                                | Compute operation probabilities         |    |

| 5                                                | Compute DG                              |    |

| 6                                                | Compute self-force, succ/pred force     |    |

| 7                                                | Schedule the operation with least force |    |

| 8                                                | until all operations are scheduled;     |    |

## 1.3 Design with HLS

We start this section by introducing of Vivado HLS from Xilinx which is used to illustrate examples in next sections [10].

## 1.3.1 Vivado High-Level Synthesis

Vivado HLS takes synthesizable C and C++/SystemC code as input and generates RTL. Vivado provides directives to optimize area, latency and throughput. In this way, the system development time is greatly reduced without the need to manually write RTL

code. The high-level synthesis process in Vivado includes three main steps: synthesis, RTL simulation and RTL implementation. In the synthesis step Verilog HDL, VHDL and SystemC code are generated based on the input code, and a report file is generated which includes design latency, resources and a interface summary of the design. In this step, various directives can be added by the designers to optimize the input code to meet the system timing and area requirements. This process is iterative, and eventually RTL code which meets the design requirements is obtained. Testbench wrappers for SystemC code and appropriate simulation scripts for Verilog and VHDL code are generated for simulation. The second step is RTL simulation to verify the behavioural functions of the RTL code. In this step, designers can simulate the SystemC code and Verilog/VHDL code with third party RTL simulators to verify the design. The third step is RTL implementation in which NGC files containing both logical design and constraints are generated for each module. Table 1.1 and in Table 1.2 listed several of these directives. For complete description, we refer [10] for details.

**Table 1.1.** Vivado HLS directives to optimize throughput and latency.

| Directive names                              | Description                                                                                                                                   |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| latency<br>loop_unroll<br>loop_flatten       | Define a minimum and/or maximum latency for a specified scope. Unroll a loop, flatten a loop, or merge loops automatically. Flatten a loop    |

| loop_merge dataflow                          | merge loops automatically.  Indicate blocks of code (functions or loops) operate concurrently.                                                |

| pipeline<br>array_partition<br>array_reshape | Pipeline the computation of a function or loop. Distribute the array across several memories. Combine partitioned arrays into a single array. |

The typical design process for Vivado will first optimize throughput and then focus on area optimizations. Area optimizations include bit-width optimization, removing design hierarchy, and limiting the number of operations. Table 1.2 describes common directives used for area optimization.

**Table 1.2.** Vivado HLS directives to optimize area.

| Directive names | Description                                                      |

|-----------------|------------------------------------------------------------------|

| allocation      | Limit the number of operations in scheduling and binding stages. |

| array_map       | Combine arrays to utilize memory more efficiently.               |

| resource        | Specify the function unit used for binding.                      |

| inline          | Allows optimization to be performed across function hierarchies. |

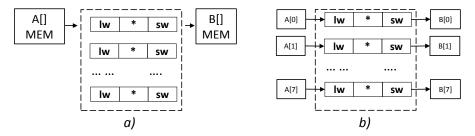

Among above directives, dataflow is one of the important features provided by Vivado HLS. The dataflow is used to implement task level parallelism (both streaming and none-streaming) of functions or loops. For example, if we need to design a system with two blocks working as follows: the first block produces an output after multiplying the input with a constant, and the second block (consumer block) reads an input from the producer and decides if input is odd or even. Task level parallelism between the producer and the consumer block is achieved by using dataflow. This means the first instance of the consumer block can be parallelized with the second instance of producer block. This increases throughput of design by a factor of 2X. When multiple tasks are parallelized as in this case, a memory is created between the producer and the consumer tasks. The memory can be a block RAM or a FIFO. If the tasks are not streaming, then a memory that is large enough to store all the output of producer must be created. if the tasks are streaming, then a FIFO must be created. In this case the size of FIFO must be large enough to store outputs of producer in a given rate. Streaming in Vivado HLS is supported by hls:: stream < TYPE > class. Here TYPE is any primitive types such as int, char or

Initiation Interval (II) as a measurement of throughput in HLS. II is used as a measurement of instruction level parallelism (provided by pipeline) or as task level parallelism (provided by dataflow). Ideally, II = 1 is the optimal and II > 1 means suboptimal. II = 1 means the task (design) can accept new data every clock cycle.

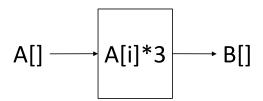

#### 1.4 HLS Hello World

In this section, we provide a brief overview of HLS design process. A HLS design must contain at least two modules. The first module is the top level design. A hardware will be generated for the top level design. The second module is the testbench. The testbench is where application programmers or HLS users write the "main()" function. Modern HLS tools (e.g., Vivado HLS) allows designers to use a C testbench to verify the functionality of top level design. Listing 1.1 and Listing 1.2 shows an example a top level design and a testbench. Design in Listing 1.1 has two inputs namely A[] and B[]. In the given codes, each of A[] and B[] has size of SIZE. Let us assume SIZE = 8 for now. Having a design like the one in Listing 1.1 is the starting point of using HLS. Next, we synthesis the top level function (in this case "'HelloWorld"'). The input to the HLS tool is a top level function, a clock period, the FPGA device and optimization directives. Depending on the target clock period, the target FPGA device and the optimization constraints, HLS tool generates different HDL code. For example, synthesizing the code in Listing 1.1 without any optimization constraints produce a sequential hardware as in Figure 1.7. Assuming the loop body takes 3 clock cycles (1 clock cycle for reading data, 1 for addition and 1 for storing the data), the loop will complete in 8\*3 = 24 clock cycles.

```

1 void HelloWorld(int A[SIZE], int B[SIZE]) {

2  #pragma HLS UNROLL factor=8

3  for(int i=0;i<SIZE;i++){

4   B[i]=A[i]+3;

5  }

6 }</pre>

```

**Listing 1.1.** HLS Hello World: HLS code for top level design

```

1

2 //Software code for verification

3 void Software_HelloWorld(int A[SIZE], int B[SIZE]) {

4  for(int i=0;i<SIZE;i++){</pre>

```

```

B[i]=A[i]+3;

}

6

7 }

9 int main() {

std::vector<int> input(SIZE, 0);

std::vector<int> output_hw(SIZE, 0);

std::vector<int> output_sw(SIZE, 0);

Boolean fail=0;

15

for(int i=0;i<SIZE;i++) {

A[i] = ,...;

16

17

18

//Call Hardware HelloWorld

19

void HelloWorld(input, output_hw);

20

21

22

//Call Software HelloWorld

void Software_HelloWorld(input, output_sw);

23

24

25

//Functionality Verification

for(int i=0;i<SIZE;i++) {</pre>

26

if(output_hw[i]!=output_sw[i]) {

27

fail=1;

28

29

}

}

30

31

if(fail==1) {

printf("'FAILED\n"');

33

34

35

printf("'PASSED\n"');

36

37

38

39

return 0;

40 }

```

Listing 1.2. HLS Hello World: HLS code for testbench

Now let us assume that we want to generate an architecture like in Figure 1.8 (a). In other words, we want to parallelize all additions and finish the computation in 3 clock cycles. This can be achieved by using *partition* and *unroll* directives provided by HLS. Using *partition* we put elements of A[] and B[] into separate memories (registers) in order

Figure 1.7. HLS Hello World Hardware Architecture

**Figure 1.8.** Hardware architectures for hello world HLS code. a) Hardware architecture created by Listing 1.1 b) Hardware architecture that we want to create.

to access them at the same clock cycle. Using *unroll* we fully unroll the loop. These optimizations can be seen in Listing 1.3. The design generated by this code finishes in 3 clock cycles. Since we are partitioning input arrays (in this case into individual elements), actual architecture will look like as in Figure 1.8 (b).

```

1 void HelloWorld(int A[SIZE], int B[SIZE]) {

2  #pragma HLS ARRAY_PARTITION variable=A complete dim=1

3  #pragma HLS ARRAY_PARTITION variable=B complete dim=1

4  for(int i=0;i<SIZE;i++) {

5  #pragma HLS UNROLL factor=8

6  B[i]=A[i]+3;

7  }

8 }</pre>

```

Listing 1.3. Optimized HLS Hello World

## 1.5 Conclusion

Increasing design cost of accelerated hardware is pushing the design community to develop tools that shorten the time-to-market duration beyond RTL design. High-Level

Synthesis has been one such a tool that provides promise in increasing productivity. In this chapter, we provided quick overview of concepts behind HLS tools and provided basic HLS optimizations with "Hello World" HLS. We demonstrated basic optimization pragma usage giving an example. While current HLS tools provide handy optimizations (pragmas) to generate optimized hardware, some real world application design flow involves several stages in order to get optimized hardware from HLS. In next chapter, we demonstrate generally accepted design flow of current HLS tool. We will do this by presenting wireless channel emulator design with HLS tool.

# Chapter 2